So lösen Sie das Problem der Wärmeableitung des Chippakets

Fortschrittliche Verpackungschips können nicht nur die Anforderungen von Hochleistungsrechnen, künstlicher Intelligenz, zunehmender Leistungsdichte usw. erfüllen, sondern auch das Wärmeableitungsproblem fortschrittlicher Verpackungen ist komplizierter geworden. Denn Hotspots auf einem Chip beeinträchtigen die Wärmeverteilung benachbarter Chips. Auch die Verbindungen zwischen Chips sind in Modulen langsamer als in SoCs.

John Parry, Branchenleiter für Elektronik und Halbleiter bei Siemens Digital Industry Software, sagte: „Bevor sich die Welt in Bereiche wie Multi-Core bewegte, hatte man es mit einem Chip zu tun, der eine maximale Leistung von etwa 150 Watt pro Quadratzentimeter hatte Eine einzelne Punktwärmequelle kann Wärme in alle drei Richtungen ableiten, sodass Sie ziemlich hohe Leistungsdichten erreichen können. Wenn Sie jedoch einen Chip daneben legen und dann einen weiteren Chip daneben legen, erwärmen sie sich Das bedeutet, dass man nicht tolerieren kann, dass jeder Chip das gleiche Leistungsniveau hat, was die thermische Herausforderung deutlich erschwert.“

Dies ist einer der Hauptgründe, warum das 3D-IC-Stacking auf dem Markt nur langsame Fortschritte macht. Während das Konzept unter dem Gesichtspunkt der Energieeffizienz und Integration sinnvoll ist – und gut in 3D-NAND und HBM funktioniert – sieht es anders aus, wenn Logik einbezogen wird. Der Logikchip erzeugt Wärme, und je dichter die Logik ist, desto höher ist die Auslastung der Verarbeitungselemente, desto größer ist die Wärme. Dies macht logisches Stapeln selten.

Wählen Sie das richtige Paket

Für Chipdesigner gibt es viele Möglichkeiten zum Verpacken. Aber die Leistung der Chip-Integration ist entscheidend. Komponenten wie Silizium-, TSV- und Kupfersäulen haben alle unterschiedliche Wärmeausdehnungskoeffizienten (TCE), was sich auf die Baugruppenausbeute und die langfristige Zuverlässigkeit auswirkt.

Das derzeit beliebte Flip-BGA-Gehäuse mit CPU und HBM hat eine Fläche von etwa 2500 Quadratmillimetern. Mike McIntyre, Leiter des Software-Produktmanagements bei Onto Innovation, sagte: „Wir sehen, dass aus einem großen Chip möglicherweise vier oder fünf kleine Chips werden. Man muss also mehr I/O haben, damit diese Chips miteinander kommunizieren können.“ So können Sie die Wärme verteilen. Letztendlich ist die Wärmeableitung ein Problem, das nur auf Systemebene gelöst werden kann und mit einer Reihe von Kompromissen verbunden ist.

Tatsächlich sind einige Geräte so komplex, dass es schwierig ist, Komponenten einfach auszutauschen, um diese Geräte an Anwendungen in bestimmten Bereichen anzupassen. Aus diesem Grund sind viele fortschrittliche Verpackungsprodukte für sehr großvolumige oder preiselastische Komponenten wie Serverchips vorgesehen.

Fortschritte bei der Simulation und Prüfung von Chipmodulen

Dennoch suchen Ingenieure nach neuen Möglichkeiten, eine thermische Analyse der Gehäusezuverlässigkeit durchzuführen, bevor die verpackten Module hergestellt werden. Beispielsweise stellt Siemens ein Beispiel für ein Dual-ASIC-basiertes Modul vor, das eine Fan-Out-Redistributionsschicht (RDL) auf einem mehrschichtigen organischen Substrat in einem BGA-Gehäuse installiert. Es werden zwei Modelle verwendet, eines für RDL-basiertes WLP und das andere für BGA mit mehrschichtigem organischem Substrat. Diese Verpackungsmodelle sind parametrisiert, umfassen Substratstapelung und BGA, bevor EDA-Informationen eingeführt werden, und ermöglichen eine frühzeitige Materialbewertung und Auswahl der Chipplatzierung. Anschließend werden die EDA-Daten importiert und für jedes Modell kann die Materialkarte eine detaillierte thermische Beschreibung der Kupferverteilung in allen Schichten liefern.

Eric Ouyang, Direktor für technisches Marketing bei JCET, verglich zusammen mit Ingenieuren von JCET und Meta die thermische Leistung von Single-Chip-, Multi-Chip-Modulen, 2,5D-Plugboards und 3D-Stapelchips mit einem ASIC und zwei Srams. [1] Der Apple-zu-Apple-Vergleich lässt die Serverumgebung, den Kühler mit Vakuumkammer und TIM unverändert. In puncto Wärme schneiden 2,5D und MCM besser ab als 3D- oder Single-Chip-Chips.

Quantisierter Wärmewiderstand

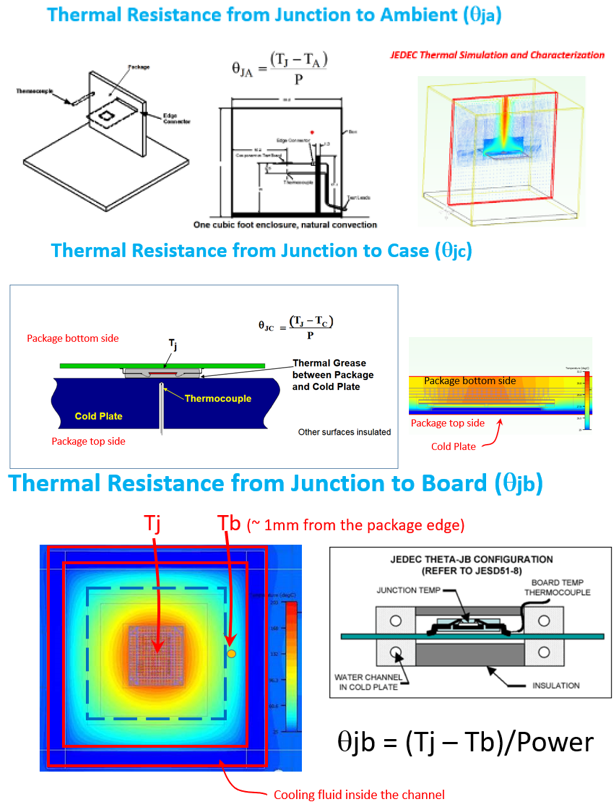

Wir können verstehen, wie Wärme durch Siliziumchips, Leiterplatten, Kleber, TIMs oder Verpackungskappen geleitet wird, und dabei die Standardmethode der Temperaturdifferenz und der Leistungsfunktion verwenden, um Temperatur- und Widerstandswerte zu verfolgen.

„Der Wärmepfad wird durch drei Schlüsselwerte quantifiziert – den Wärmewiderstand vom Geräteknoten zur Umgebung, den Wärmewiderstand vom Knoten zum Gehäuse [an der Oberseite des Gehäuses] und den Wärmewiderstand vom Knoten zur Platine „, sagt Ouyang von JCET. Zumindest, betont er, benötigen die Kunden von JCET ɵja, ɵjc und ɵjb, die sie dann im Systemdesign verwenden. Sie können verlangen, dass ein bestimmter Wärmewiderstand einen bestimmten Wert nicht überschreitet und dass das Gehäusedesign diese Leistung bietet.

Die thermische Simulation ist die wirtschaftlichste Möglichkeit, die Auswahl und Zusammenstellung von Materialien zu untersuchen. Durch die Simulation des Chips im Betriebszustand finden wir normalerweise einen oder mehrere Hotspots, sodass wir dem Substrat unterhalb des Hotspots Kupfer hinzufügen können, um die Wärmeableitung zu erleichtern. Oder das Verpackungsmaterial wechseln, den Kühler vergrößern. Der Systemintegrator kann festlegen, dass die Wärmewiderstände ɵja, ɵjc und ɵjb bestimmte Werte nicht überschreiten dürfen. Unter normalen Umständen sollte die Temperatur der Siliziumverbindung unter 125 °C gehalten werden. Nach Abschluss der Simulation führt die Verpackungsanlage eine Versuchsplanung (DOE) durch, um zum endgültigen Verpackungsplan zu gelangen.

Wählen Sie TIM

Im Gehäuse werden mehr als 90 % der Wärme durch das Gehäuse von der Oberseite des Chips zum Kühler abgeleitet, bei dem es sich normalerweise um eine vertikale Rippe aus eloxiertem Aluminium handelt. Zwischen Chip und Gehäuse werden thermische Schnittstellenmaterialien (TIM) mit hoher Wärmeleitfähigkeit platziert, um die Wärmeübertragung zu unterstützen. TIM der nächsten Generation für CPUs umfassen Blechlegierungen wie Indium und Zinn sowie silbergesintertes Zinn mit einer Leitfähigkeit von 60 W/mK bzw. 50 W/mK. Da Anbieter SoCs auf Chiplet-Prozesse umstellen, werden mehr TIMs mit unterschiedlichen Eigenschaften und Dicken benötigt.

YoungDo Kweon, leitender Direktor für Forschung und Entwicklung bei Amkor, sagte, dass bei Systemen mit hoher Dichte der thermische Widerstand des TIM zwischen Chip und Gehäuse einen größeren Einfluss auf den gesamten thermischen Widerstand des verpackten Moduls habe. Die Leistungstrends nehmen dramatisch zu, insbesondere im Logikbereich. Daher konzentrieren wir uns darauf, die Sperrschichttemperatur niedrig zu halten, um einen zuverlässigen Halbleiterbetrieb sicherzustellen. Während TIM-Lieferanten Wärmewiderstandswerte für ihre Materialien angeben, wird der Wärmewiderstand vom Chip zum Gehäuse (ɵjc) in Wirklichkeit durch den Montageprozess selbst beeinflusst, einschließlich der Verbindungsqualität und der Kontaktfläche zwischen Chip und TIM. Er weist darauf hin, dass Tests mit tatsächlichen Montagewerkzeugen und Verbindungsmaterialien in einer kontrollierten Umgebung von entscheidender Bedeutung sind, um die tatsächlichen thermischen Eigenschaften zu verstehen und das beste TIM für die Kundenverifizierung auszuwählen.

Auf unterschiedliche Weise mit Hitze umgehen

Chiphersteller suchen nach Möglichkeiten, das Problem der Wärmeableitung zu lösen. Randy White, Programmmanager für Speicherlösungen bei Keysight Technologies, sagte: „Das Paket ist das gleiche, wenn man die Chipgröße um ein Viertel reduziert, wird es schneller. Dies kann zu einigen Signalintegritätsunterschieden führen. Wegen der Bonding-Linie.“ Je länger die Leitung ist, desto größer ist die Induktivität. Wie kann man also auf ausreichend kleinem Raum so viel Energie verbrauchen? studiert.“ Dies hat zu erheblichen Investitionen in die hochmoderne Bondforschung geführt, die sich offenbar auf Hybridbonding konzentriert. Allerdings sind die Kosten für Hybrid-Bonding hoch und es ist immer noch auf Hochleistungsprozessoranwendungen beschränkt, wobei TSMC eines der wenigen Unternehmen ist, das diese Technologie derzeit anbietet. Die Aussicht, Photonen auf CMOS-Chips oder siliziumbasiertem Galliumnitrid zu vereinen, ist jedoch vielversprechend.

Fountyl Technologies PTE Ltd konzentriert sich auf die Halbleiterfertigungsindustrie. Zu den Hauptprodukten gehören: Stiftfutter, poröses Keramikfutter, Keramik-Endeffektor, Keramik-Vierkantbalken, Keramikspindel. Willkommen bei Kontakt und Verhandlung!