Cómo resolver el problema de disipación de calor del paquete de chips

Los chips de embalaje avanzados no solo pueden satisfacer las necesidades de la informática de alto rendimiento, la inteligencia artificial, el crecimiento de la densidad de potencia, etc., sino que también el problema de la disipación de calor del embalaje avanzado se ha vuelto complicado. Porque los puntos calientes en un chip afectan la distribución del calor de los chips vecinos. Las interconexiones entre chips también son más lentas en los módulos que en los SoC.

John Parry, jefe de la industria de electrónica y semiconductores de Siemens Digital Industry Software, dijo: "Antes de que el mundo pasara a áreas como el multinúcleo, se trataba de un chip que tenía una potencia máxima de aproximadamente 150 vatios por centímetro cuadrado, que era Una fuente de calor de un solo punto puede disipar el calor en las tres direcciones, por lo que puede lograr densidades de potencia bastante altas. Pero cuando tienes un chip, colocas otro chip al lado y luego colocas otro chip al lado, se calientan. entre sí. Eso significa que no se puede tolerar que cada chip tenga el mismo nivel de potencia, lo que hace que el desafío térmico sea mucho más difícil".

Esta es una de las principales razones por las que el apilamiento de 3D-IC está avanzando lentamente en el mercado. Si bien el concepto tiene sentido desde el punto de vista de la integración y la eficiencia energética (y funciona bien en 3D NAND y HBM), la historia es diferente cuando se incluye la lógica. El chip lógico genera calor y cuanto más densa es la lógica, mayor es la utilización de los elementos de procesamiento y mayor es el calor. Esto hace que el apilamiento lógico sea poco común.

Elija el paquete correcto

Para los diseñadores de chips, hay muchas formas de empaquetar. Pero el rendimiento de la integración de chips es crucial. Componentes como las columnas de silicio, TSV y cobre tienen diferentes coeficientes de expansión térmica (TCE), lo que afecta el rendimiento del ensamblaje y la confiabilidad a largo plazo.

El popular paquete flip BGA actual con CPU y HBM tiene un área de aproximadamente 2500 milímetros cuadrados. Mike McIntyre, jefe de gestión de productos de software de Onto Innovation, dijo: "Estamos viendo que un chip grande puede convertirse en cuatro o cinco chips pequeños. Por lo tanto, es necesario tener más E/S para que estos chips se comuniquen entre sí. Para poder distribuir el calor En última instancia, la disipación de calor es un problema que sólo puede abordarse a nivel del sistema y conlleva una serie de compensaciones.

De hecho, algunos dispositivos son tan complejos que es difícil reemplazar componentes fácilmente para personalizarlos para aplicaciones en campos específicos. Esta es la razón por la que muchos productos de embalaje avanzados son para componentes de muy alto volumen o de precio elástico, como los chips de servidor.

Progresos en simulación y prueba de módulos de chip

Sin embargo, los ingenieros están buscando nuevas formas de realizar análisis térmicos de la confiabilidad del paquete antes de fabricar los módulos empaquetados. Por ejemplo, Siemens proporciona un ejemplo de un módulo dual basado en ASIC que instala una capa de redistribución en abanico (RDL) en un sustrato orgánico multicapa en un paquete BGA. Utiliza dos modelos, uno para WLP basado en RDL y el otro para sustrato orgánico multicapa BGA. Estos modelos de empaque están parametrizados, incluyen apilamiento de sustratos y BGA antes de que se introduzca la información EDA y permiten una evaluación temprana del material y la selección de la ubicación del chip. A continuación, se importan los datos de EDA y, para cada modelo, el mapa de materiales puede proporcionar una descripción térmica detallada de la distribución del cobre en todas las capas.

Eric Ouyang, director de marketing técnico de JCET, junto con ingenieros de JCET y Meta, compararon el rendimiento térmico de módulos de un solo chip y de varios chips, placas de conexión 2,5D y chips apilados 3D con un ASIC y dos Srams. [1] La comparación Apple-Apple no modifica el entorno del servidor, el radiador con cámara de vacío ni el TIM. En términos de calor, 2.5D y MCM funcionan mejor que los chips 3D o de un solo chip.

Resistencia térmica cuantificada

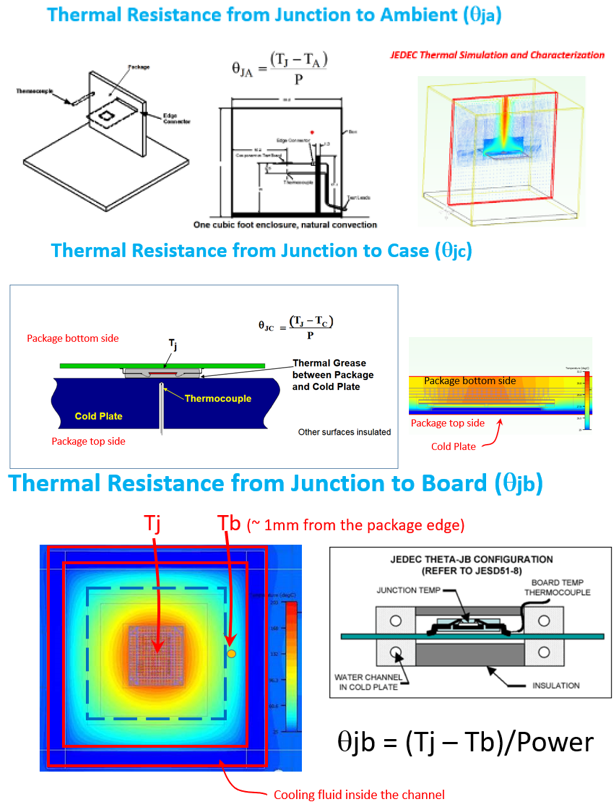

Podemos entender cómo se conduce el calor a través de chips de silicio, placas de circuitos, pegamentos, TIM o tapas de embalaje, mientras utilizamos el método estándar de diferencia de temperatura y función de potencia para rastrear los valores de temperatura y resistencia.

"La ruta térmica se cuantifica mediante tres valores clave: la resistencia térmica desde el nodo del dispositivo al medio ambiente, la resistencia térmica desde el nodo a la carcasa [en la parte superior del paquete] y la resistencia térmica desde el nodo a la placa. ," dice Ouyang de JCET. Como mínimo, señala, los clientes de JCET necesitan ɵja, ɵjc y ɵjb, que luego utilizan en el diseño del sistema. Es posible que requieran que una resistencia térmica determinada no supere un valor específico y que el diseño del paquete proporcione ese rendimiento.

La simulación térmica es la forma más económica de explorar la selección y colocación de materiales. Al simular el chip en estado de funcionamiento, generalmente encontramos uno o más puntos calientes, por lo que podemos agregar cobre al sustrato debajo del punto caliente para facilitar la disipación del calor; O cambie el material de embalaje, aumente el radiador. El integrador del sistema puede especificar que la resistencia térmica ɵja, ɵjc y ɵjb no debe exceder ciertos valores. En circunstancias normales, la temperatura de la unión de silicio debe mantenerse por debajo de 125 °C. Una vez completada la simulación, la planta de envasado lleva a cabo un diseño de experimentos (DOE) para llegar al plan de envasado final.

Seleccione TIEMPO

En el paquete, más del 90% del calor se disipa a través del paquete desde la parte superior del chip hasta el radiador, que suele ser una aleta vertical a base de aluminio anodizado. Se colocan materiales de interfaz térmica (TIM) con alta conductividad térmica entre el chip y el paquete para ayudar a transferir calor. Los TIM de próxima generación para CPU incluyen aleaciones de chapa como indio y estaño, así como estaño sinterizado con plata con una conductividad de 60 W/mK y 50 W/mK, respectivamente. A medida que los proveedores realizan la transición de SoC a procesos de chiplet, se necesitan más TIM con diferentes propiedades y espesores.

YoungDo Kweon, director senior de investigación y desarrollo de Amkor, dijo que para sistemas de alta densidad, la resistencia térmica del TIM entre el chip y el paquete tiene un mayor impacto en la resistencia térmica general del módulo empaquetado. Las tendencias energéticas están aumentando drásticamente, especialmente en el caso de la lógica, por lo que nos centramos en mantener baja la temperatura de la unión para garantizar un funcionamiento fiable de los semiconductores. Si bien los proveedores de TIM proporcionan valores de resistencia térmica para sus materiales, en realidad, la resistencia térmica del chip al paquete (ɵjc) se ve afectada por el proceso de ensamblaje en sí, incluida la calidad de la unión y el área de contacto entre el chip y el TIM. Señala que las pruebas con herramientas de ensamblaje reales y materiales de unión en un entorno controlado son fundamentales para comprender las propiedades térmicas reales y seleccionar el mejor TIM para la verificación del cliente.

Cómo lidiar con el calor de diferentes maneras

Los fabricantes de chips están buscando formas de resolver el problema de la disipación de calor. Randy White, director de programas para soluciones de memoria de Keysight Technologies, dijo: "El paquete es el mismo, si reduce el área del tamaño del chip en una cuarta parte, se acelerará. Esto puede dar lugar a algunas diferencias en la integridad de la señal. Debido a que la línea de unión del paquete externo entrará al chip, cuanto más larga sea la línea, mayor será la inductancia, por lo que hay una parte del rendimiento eléctrico. Entonces, ¿cómo se consume tanta energía en un espacio lo suficientemente pequeño? Este es otro parámetro clave que debe analizarse. estudió." Esto ha llevado a una inversión significativa en investigaciones de vanguardia sobre bonos que parecen centrarse en los bonos híbridos. Pero el costo de la vinculación híbrida es alto y todavía se limita a aplicaciones de tipo procesador de alto rendimiento, siendo TSMC una de las únicas empresas que actualmente ofrece esta tecnología. Sin embargo, la posibilidad de combinar fotones en chips CMOS o nitruro de galio a base de silicio es muy prometedora.

Fountyl Technologies PTE Ltd, se centra en la industria de fabricación de semiconductores, sus principales productos incluyen: mandril de pasador, mandril de cerámica porosa, efector final de cerámica, viga cuadrada de cerámica, husillo de cerámica, ¡bienvenido a contactar y negociar!