چگونه مشکل اتلاف حرارت بسته تراشه را حل کنیم

تراشه های بسته بندی پیشرفته نه تنها می توانند نیازهای محاسباتی با کارایی بالا، هوش مصنوعی، رشد چگالی توان و غیره را برآورده کنند، بلکه مشکل اتلاف گرما بسته بندی های پیشرفته نیز پیچیده شده است. زیرا نقاط داغ روی یک تراشه بر توزیع گرمای تراشه های همسایه تأثیر می گذارد. اتصالات بین تراشه ها نیز در ماژول ها کندتر از SoC ها است.

جان پری، رئیس صنعت الکترونیک و نیمههادیها در نرمافزار صنعت دیجیتال زیمنس، میگوید: «قبل از اینکه دنیا به سمت حوزههایی مانند چند هستهای حرکت کند، شما با تراشهای مواجه بودید که حداکثر توان آن حدود 150 وات بر سانتیمتر مربع بود. یک منبع حرارتی تک نقطه ای می توانید گرما را در هر سه جهت پخش کنید، بنابراین می توانید به چگالی توان بسیار بالایی دست پیدا کنید، اما وقتی یک تراشه دارید، یک تراشه دیگر در کنار آن قرار دهید، آنها گرم می شوند این بدان معناست که شما نمی توانید تحمل کنید که هر تراشه یک سطح قدرت داشته باشد، که چالش حرارتی را بسیار دشوارتر می کند.

این یکی از دلایل اصلی است که چرا انباشته شدن آی سی سه بعدی در حال پیشرفت کند در بازار است. در حالی که این مفهوم از نقطه نظر بهره وری انرژی و یکپارچگی منطقی است - و در 3D NAND و HBM به خوبی کار می کند - وقتی منطق گنجانده شود داستان متفاوتی است. تراشه منطقی گرما تولید می کند، و هر چه منطق متراکم تر باشد، استفاده از عناصر پردازش بیشتر، گرما بیشتر می شود. این باعث می شود انباشته شدن منطقی نادر باشد.

بسته مناسب را انتخاب کنید

برای طراحان تراشه، راه های زیادی برای بسته بندی وجود دارد. اما عملکرد یکپارچه سازی تراشه بسیار مهم است. قطعاتی مانند سیلیکون، TSV و ستونهای مسی همگی دارای ضریب انبساط حرارتی (TCE) متفاوتی هستند که بر بازده مونتاژ و قابلیت اطمینان طولانیمدت تأثیر میگذارد.

پکیج محبوب فلیپ BGA فعلی با cpu و HBM مساحتی در حدود 2500 میلی متر مربع دارد. مایک مک اینتایر، رئیس مدیریت محصولات نرمافزاری Onto Innovation، میگوید: "ما شاهد یک تراشه بزرگ هستیم که به طور بالقوه به چهار یا پنج تراشه کوچک تبدیل میشود. بنابراین برای اینکه این تراشهها بتوانند با یکدیگر صحبت کنند، باید I/O بیشتری داشته باشید. بنابراین شما می توانید گرما را توزیع کنید در نهایت، اتلاف گرما مشکلی است که فقط در سطح سیستم قابل حل است و با یک سری معاوضه همراه است.

در واقع، برخی از دستگاه ها به قدری پیچیده هستند که جایگزینی آسان اجزا برای سفارشی کردن این دستگاه ها برای برنامه های کاربردی در زمینه های خاص دشوار است. به همین دلیل است که بسیاری از محصولات بسته بندی پیشرفته برای اجزای بسیار با حجم بالا یا انعطاف پذیر قیمت مانند تراشه های سرور هستند.

پیشرفت در شبیه سازی و آزمایش ماژول تراشه

با این وجود، مهندسان به دنبال راههای جدیدی برای انجام تحلیل حرارتی قابلیت اطمینان پکیج قبل از تولید ماژولهای بستهبندی شده هستند. برای مثال، زیمنس نمونهای از یک ماژول مبتنی بر ASIC دوگانه را ارائه میکند که یک لایه توزیع مجدد بادکنک (RDL) را روی یک بستر آلی چند لایه در یک بسته BGA نصب میکند. از دو مدل استفاده می کند، یکی برای WLP مبتنی بر RDL و دیگری برای BGA بستر آلی چند لایه. این مدلهای بستهبندی پارامتری هستند، شامل انباشته شدن بستر و BGA قبل از معرفی اطلاعات EDA میشوند و ارزیابی اولیه مواد و انتخاب قرار دادن تراشه را امکانپذیر میسازند. سپس دادههای EDA وارد میشوند و برای هر مدل، نقشه مواد قادر به ارائه توضیحات حرارتی دقیق از توزیع مس در تمام لایهها است.

اریک اویانگ، مدیر بازاریابی فنی در JCET، به همراه مهندسان JCET و Meta، عملکرد حرارتی ماژول های تک تراشه، چند تراشه، پلاگین های 2.5 بعدی و تراشه های انباشته سه بعدی را با یک ASIC و دو Sram مقایسه کردند. [1] مقایسه Apple-to-Apple محیط سرور، رادیاتور با محفظه خلاء و TIM را بدون تغییر باقی می گذارد. از نظر گرما، 2.5D و MCM عملکرد بهتری نسبت به تراشه های سه بعدی یا تک چیپ دارند.

مقاومت حرارتی کوانتیزه

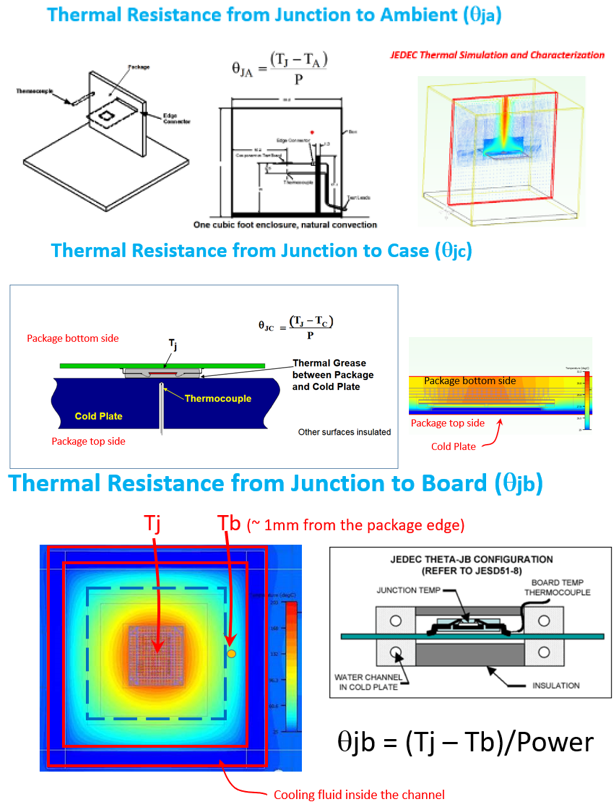

ما می توانیم درک کنیم که چگونه گرما از طریق تراشه های سیلیکونی، تخته های مدار، چسب ها، TIM ها یا درپوش های بسته بندی هدایت می شود، در حالی که از روش استاندارد تفاوت دما و عملکرد توان برای ردیابی دما و مقادیر مقاومت استفاده می کنیم.

"مسیر حرارتی با سه مقدار کلیدی تعیین می شود - مقاومت حرارتی از گره دستگاه به محیط، مقاومت حرارتی از گره به محفظه [در بالای بسته]، و مقاومت حرارتی از گره به برد. اویانگ از JCET می گوید. او اشاره می کند که حداقل، مشتریان JCET به ɵja، ɵjc و ɵjb نیاز دارند که سپس در طراحی سیستم از آنها استفاده می کنند. آنها ممکن است نیاز داشته باشند که یک مقاومت حرارتی معین از یک مقدار خاص تجاوز نکند و طراحی بسته آن عملکرد را ارائه دهد.

شبیه سازی حرارتی مقرون به صرفه ترین راه برای کشف انتخاب و همنشینی مواد است. از طریق شبیه سازی تراشه در حالت کار، ما معمولا یک یا چند نقطه داغ پیدا می کنیم، بنابراین می توانیم مس را به بستر زیر نقطه داغ اضافه کنیم تا اتلاف گرما را تسهیل کنیم. یا مواد بسته بندی را تغییر دهید، رادیاتور را افزایش دهید. یکپارچه ساز سیستم ممکن است مشخص کند که مقاومت حرارتی ɵja، ɵjc و ɵjb نباید از مقادیر خاصی تجاوز کند. در شرایط عادی، دمای محل اتصال سیلیکون باید زیر 125 درجه سانتیگراد نگه داشته شود. پس از تکمیل شبیه سازی، کارخانه بسته بندی یک طراحی آزمایشی (DOE) را برای رسیدن به طرح بسته نهایی انجام می دهد.

TIM را انتخاب کنید

در بسته، بیش از 90 درصد گرما از طریق بسته بندی از بالای تراشه به رادیاتور که معمولاً یک باله عمودی بر پایه آلومینیوم آنودایز است، پخش می شود. مواد رابط حرارتی (TIM) با رسانایی حرارتی بالا بین تراشه و بسته قرار می گیرند تا به انتقال گرما کمک کنند. نسل بعدی TIM برای cpus شامل آلیاژهای ورق فلزی مانند ایندیم و قلع و همچنین قلع پخته شده با نقره با رسانایی به ترتیب 60W/mK و 50W/mK است. همانطور که فروشندگان SoC ها را به فرآیندهای چیپلت منتقل می کنند، TIM های بیشتری با ویژگی ها و ضخامت های متفاوت مورد نیاز است.

YoungDo Kweon، مدیر ارشد تحقیق و توسعه در Amkor، گفت که برای سیستمهای با چگالی بالا، مقاومت حرارتی TIM بین تراشه و بستهبندی تأثیر بیشتری بر مقاومت حرارتی کلی ماژول بستهبندی شده دارد. روند قدرت به طور چشمگیری افزایش می یابد، به ویژه برای منطق، بنابراین ما بر پایین نگه داشتن دمای اتصال تمرکز می کنیم تا عملکرد نیمه هادی قابل اعتماد را تضمین کنیم. در حالی که تامین کنندگان TIM مقادیر مقاومت حرارتی را برای مواد خود ارائه می دهند، در واقع، مقاومت حرارتی از تراشه به بسته (ɵjc) تحت تأثیر خود فرآیند مونتاژ، از جمله کیفیت اتصال و ناحیه تماس بین تراشه و TIM قرار می گیرد. او خاطرنشان می کند که آزمایش با ابزارهای مونتاژ واقعی و مواد اتصال در یک محیط کنترل شده برای درک خواص حرارتی واقعی و انتخاب بهترین TIM برای تأیید مشتری ضروری است.

برای مقابله با گرما به روش های مختلف

سازندگان تراشه به دنبال راه هایی برای حل مشکل اتلاف گرما هستند. رندی وایت، مدیر برنامه راه حل های حافظه در Keysight Technologies، گفت: "بسته یکسان است، اگر اندازه تراشه را یک چهارم کاهش دهید، سرعت آن افزایش می یابد. این ممکن است منجر به برخی تفاوت های یکپارچگی سیگنال شود. زیرا خط اتصال بسته خارجی وارد تراشه میشود، هر چه خط طولانیتر باشد، اندوکتانس بیشتری دارد، بنابراین چگونه میتوانید آنقدر انرژی در یک فضای کوچک مصرف کنید مطالعه کرد." این امر منجر به سرمایه گذاری قابل توجهی در تحقیقات پیشرفته پیوند شده است که به نظر می رسد بر پیوند هیبریدی تمرکز دارد. اما هزینه پیوند هیبریدی بالا است و هنوز هم محدود به برنامه های کاربردی از نوع پردازشگر با کارایی بالا است و TSMC یکی از تنها شرکت هایی است که در حال حاضر این فناوری را ارائه می دهد. با این حال، چشم انداز ترکیب فوتون ها بر روی تراشه های CMOS یا نیترید گالیوم مبتنی بر سیلیکون بسیار امیدوارکننده است.

Fountyl Technologies PTE Ltd، بر صنعت تولید نیمه هادی تمرکز دارد، محصولات اصلی عبارتند از: پین چاک، چاک سرامیکی متخلخل، افکتور انتهایی سرامیکی، پرتو مربع سرامیکی، دوک سرامیکی، خوش آمدید به تماس و مذاکره!