Comment résoudre le problème de dissipation thermique du paquet de puces

Les puces d'emballage avancées peuvent non seulement répondre aux besoins du calcul haute performance, de l'intelligence artificielle, de la croissance de la densité de puissance, etc., mais le problème de dissipation thermique des emballages avancés est également devenu compliqué. Parce que les points chauds sur une puce affectent la répartition de la chaleur des puces voisines. Les interconnexions entre puces sont également plus lentes dans les modules que dans les SoC.

John Parry, responsable de l'industrie de l'électronique et des semi-conducteurs chez Siemens Digital Industry Software, a déclaré : « Avant que le monde ne s'oriente vers des domaines comme le multicœur, vous aviez affaire à une puce qui avait une puissance maximale d'environ 150 watts par centimètre carré, ce qui était une source de chaleur unique. Vous pouvez dissiper la chaleur dans les trois directions, vous pouvez donc atteindre des densités de puissance assez élevées. Mais lorsque vous avez une puce, placez une autre puce à côté, puis placez une autre puce à côté, elles chauffent. Cela signifie que vous ne pouvez pas tolérer que chaque puce ait le même niveau de puissance, ce qui rend le défi thermique beaucoup plus difficile.

C’est l’une des principales raisons pour lesquelles l’empilement de circuits intégrés 3D progresse lentement sur le marché. Bien que le concept ait du sens du point de vue de l’efficacité énergétique et de l’intégration – et fonctionne bien en 3D NAND et HBM – c’est une autre histoire lorsque la logique est incluse. La puce logique génère de la chaleur, et plus la logique est dense, plus l'utilisation des éléments de traitement est élevée, plus la chaleur est importante. Cela rend l’empilement logique rare.

Choisissez le bon forfait

Pour les concepteurs de puces, il existe de nombreuses façons de conditionner. Mais la performance de l’intégration des puces est cruciale. Les composants tels que les colonnes en silicium, TSV et cuivre ont tous un coefficient de dilatation thermique (TCE) différent, ce qui affecte le rendement de l'assemblage et la fiabilité à long terme.

Le package flip BGA populaire actuel avec processeur et HBM a une superficie d'environ 2 500 millimètres carrés. Mike McIntyre, responsable de la gestion des produits logiciels chez Onto Innovation, a déclaré : « Nous voyons une grosse puce devenir potentiellement quatre ou cinq petites puces. Il faut donc avoir plus d'E/S pour que ces puces communiquent entre elles. Vous pouvez ainsi répartir la chaleur. En fin de compte, la dissipation thermique est un problème qui ne peut être résolu qu'au niveau du système, et qui s'accompagne d'une série de compromis.

En fait, certains appareils sont si complexes qu’il est difficile de remplacer facilement des composants afin de personnaliser ces appareils pour des applications dans des domaines spécifiques. C'est pourquoi de nombreux produits d'emballage avancés sont destinés à des composants à très haut volume ou dont le prix est élastique, tels que les puces de serveur.

Progrès dans la simulation et les tests de modules à puce

Néanmoins, les ingénieurs recherchent de nouvelles façons d'effectuer une analyse thermique de la fiabilité des boîtiers avant la fabrication des modules conditionnés. Par exemple, Siemens fournit un exemple de module double basé sur ASIC qui installe une couche de redistribution de sortance (RDL) sur un substrat organique multicouche dans un boîtier BGA. Il utilise deux modèles, l'un pour le WLP basé sur RDL et l'autre pour le substrat organique multicouche BGA. Ces modèles de boîtier sont paramétrés, incluent l'empilement de substrats et le BGA avant l'introduction des informations EDA, et permettent une évaluation précoce des matériaux et une sélection précoce du placement des puces. Ensuite, les données EDA sont importées et, pour chaque modèle, la carte des matériaux est capable de fournir une description thermique détaillée de la répartition du cuivre dans toutes les couches.

Eric Ouyang, directeur du marketing technique chez JCET, en collaboration avec des ingénieurs de JCET et Meta, a comparé les performances thermiques de modules monopuces, multipuces, de cartes de connexion 2,5D et de puces empilées 3D avec un ASIC et deux Sram. [1] La comparaison Apple-to-Apple laisse l'environnement du serveur, le radiateur avec chambre à vide et le TIM inchangés. En termes de chaleur, les puces 2,5D et MCM fonctionnent mieux que les puces 3D ou monopuces.

Résistance thermique quantifiée

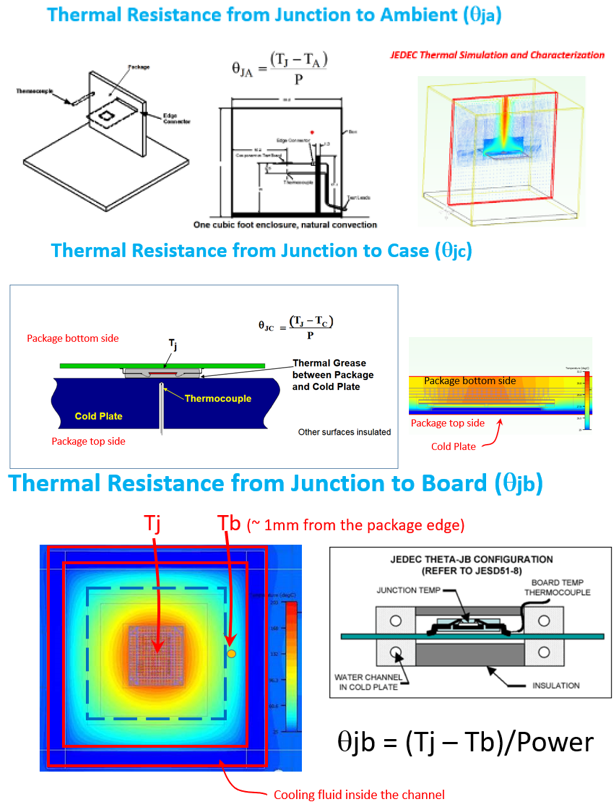

Nous pouvons comprendre comment la chaleur est conduite à travers les puces de silicium, les circuits imprimés, les colles, les TIM ou les bouchons d'emballage, tout en utilisant la méthode standard de différence de température et de fonction de puissance pour suivre les valeurs de température et de résistance.

"Le chemin thermique est quantifié par trois valeurs clés : la résistance thermique du nœud de l'appareil à l'environnement, la résistance thermique du nœud au boîtier [en haut du boîtier] et la résistance thermique du nœud à la carte. ", déclare Ouyang du JCET. À tout le moins, souligne-t-il, les clients de JCET ont besoin de ɵja, ɵjc et ɵjb, qu'ils utilisent ensuite dans la conception du système. Ils peuvent exiger qu'une résistance thermique donnée ne dépasse pas une valeur spécifique et que la conception du boîtier offre cette performance.

La simulation thermique est le moyen le plus économique d’explorer la sélection et la colocalisation des matériaux. Grâce à la simulation de la puce en état de fonctionnement, nous trouvons généralement un ou plusieurs points chauds, nous pouvons donc ajouter du cuivre au substrat sous le point chaud pour faciliter la dissipation thermique ; Ou changez le matériau d'emballage, augmentez le radiateur. L'intégrateur système peut préciser que les résistances thermiques ɵja, ɵjc et ɵjb ne doivent pas dépasser certaines valeurs. Dans des circonstances normales, la température de jonction du silicium doit être maintenue en dessous de 125 °C. Une fois la simulation terminée, l'usine de conditionnement réalise un plan d'expériences (DOE) pour arriver au plan de colis final.

Sélectionnez TIM

Dans le boîtier, plus de 90 % de la chaleur est dissipée à travers le boîtier, depuis le haut de la puce jusqu'au radiateur, qui est généralement une ailette verticale à base d'aluminium anodisé. Des matériaux d'interface thermique (TIM) à haute conductivité thermique sont placés entre la puce et le boîtier pour faciliter le transfert de chaleur. Les TIM de nouvelle génération pour processeurs comprennent des alliages de tôle tels que l'indium et l'étain, ainsi que de l'étain fritté à l'argent avec une conductivité de 60 W/mK et 50 W/mK, respectivement. À mesure que les fournisseurs font la transition des SoC vers des processus chiplet, davantage de TIM avec des propriétés et des épaisseurs différentes sont nécessaires.

YoungDo Kweon, directeur principal de la recherche et du développement chez Amkor, a déclaré que pour les systèmes haute densité, la résistance thermique du TIM entre la puce et le boîtier a un impact plus important sur la résistance thermique globale du module emballé. Les tendances en matière de puissance augmentent considérablement, en particulier pour la logique, c'est pourquoi nous nous concentrons sur le maintien d'une température de jonction basse pour garantir un fonctionnement fiable des semi-conducteurs. Alors que les fournisseurs de TIM fournissent des valeurs de résistance thermique pour leurs matériaux, en réalité, la résistance thermique de la puce au boîtier (ɵjc) est affectée par le processus d'assemblage lui-même, y compris la qualité de la liaison et la zone de contact entre la puce et le TIM. Il note que les tests avec des outils d'assemblage et des matériaux de liaison réels dans un environnement contrôlé sont essentiels pour comprendre les propriétés thermiques réelles et sélectionner le meilleur TIM pour la vérification par le client.

Gérer la chaleur de différentes manières

Les fabricants de puces recherchent des moyens de résoudre le problème de la dissipation thermique. Randy White, responsable du programme pour les solutions de mémoire chez Keysight Technologies, a déclaré : « Le package est le même. Si vous réduisez la taille de la puce d'un quart, cela accélérera. Cela peut entraîner certaines différences d'intégrité du signal. Parce que la ligne de liaison du boîtier externe entrera dans la puce, plus la ligne est longue, plus l'inductance est grande, il y a donc une partie de performance électrique. Alors, comment consommer autant d'énergie dans un espace suffisamment petit ? étudié." Cela a conduit à des investissements importants dans la recherche de pointe sur les obligations, qui semblent se concentrer sur les obligations hybrides. Mais le coût de la liaison hybride est élevé, et il reste encore limité aux applications de type processeur hautes performances, TSMC étant l'une des seules sociétés à proposer actuellement cette technologie. Cependant, la perspective de combiner des photons sur des puces CMOS ou du nitrure de gallium à base de silicium est très prometteuse.

Fountyl Technologies PTE Ltd, se concentre sur l'industrie de fabrication de semi-conducteurs, les principaux produits comprennent : mandrin à broches, mandrin en céramique poreuse, effecteur d'extrémité en céramique, poutre carrée en céramique, broche en céramique, bienvenue au contact et à la négociation !