चिप उद्योग. तकनीकी शब्द और संक्षिप्तीकरण. संज्ञाओं का ग्राफिक विश्लेषण

उत्पादन

टेपआउट(TO): इसका अर्थ है प्रसंस्करण के लिए अंतिम GDSII फ़ाइल को फाउंड्री में जमा करना।

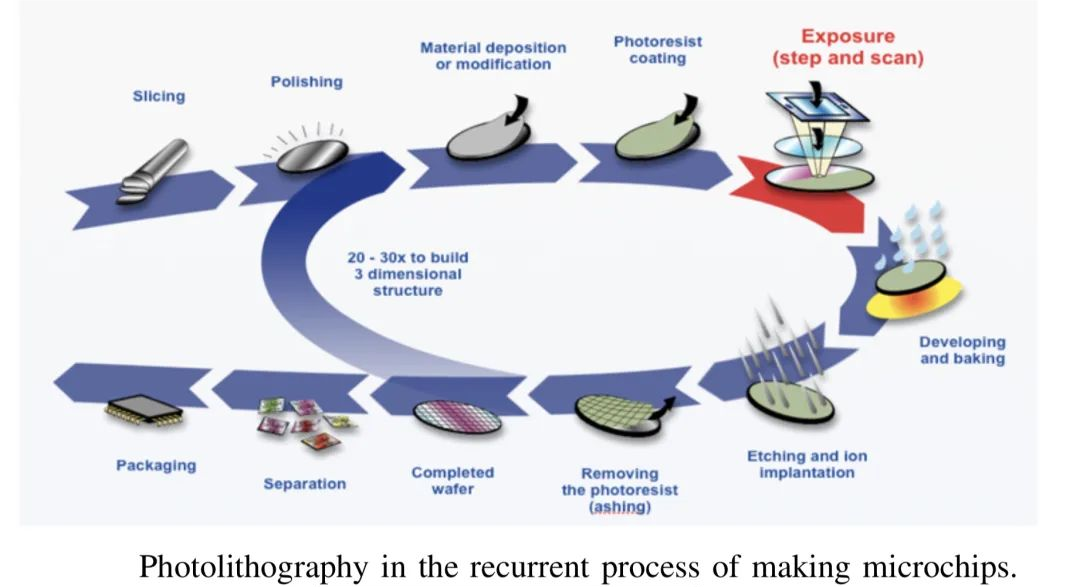

पूर्ण मास्क: अर्थात, विनिर्माण प्रक्रिया में सभी मास्क एक निश्चित डिज़ाइन प्रदान करते हैं।

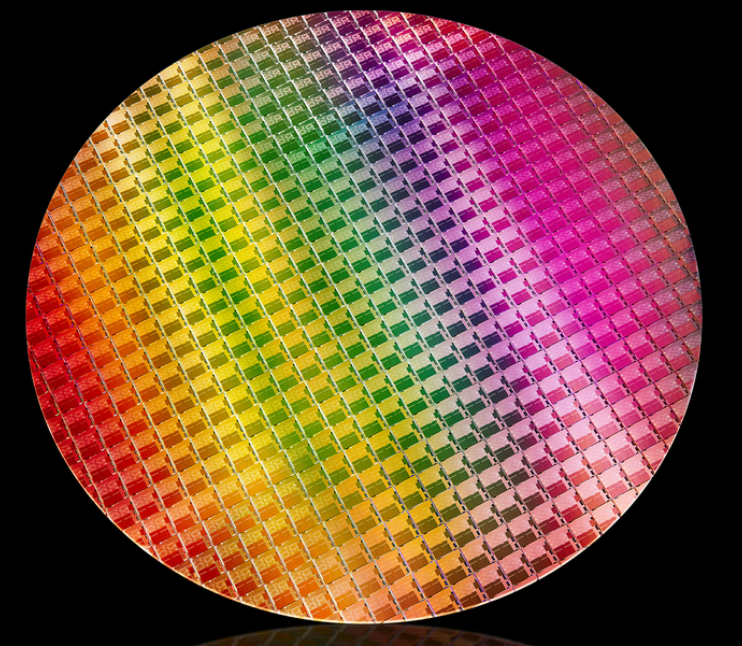

एमपीडब्ल्यू (मल्टी प्रोजेक्ट वेफर):यानी, कई परियोजनाएं एक वेफर साझा करती हैं, यानी एक ही विनिर्माण प्रक्रिया कई आईसी डिजाइनों के निर्माण का कार्य कर सकती है।

MPW को अन्य निर्माताओं के साथ MASK प्लेट साझा करना है, और FULL MASK को अकेले मास्क प्लेट का आनंद लेना है। यदि चिप का जोखिम अपेक्षाकृत अधिक है, तो आप पहले एमपीडब्ल्यू कर सकते हैं, यदि परीक्षण में कोई समस्या नहीं है, और फिर फुल मास्क करें।

फाउंड्री:विशेष ताइवान सेमीकंडक्टर मैन्युफैक्चरिंग (टीएसएमसी), सेमीकंडक्टर मैन्युफैक्चरिंग इंटरनेशनल (एसएमआईसी), यूनाइटेड इलेक्ट्रिक (यूएमसी) जैसे चिप निर्माण निर्माताओं में एड। संगत फैबलेस है, डिज़ाइन निर्माता है, बस कोई फैब नहीं है।

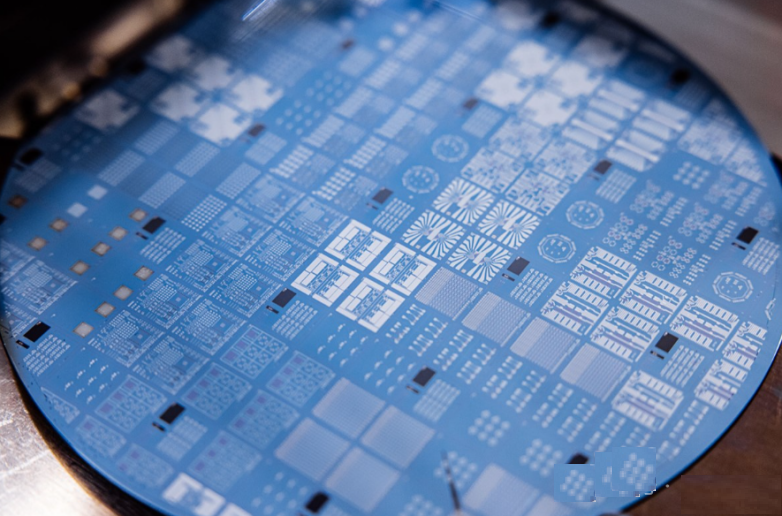

वफ़र

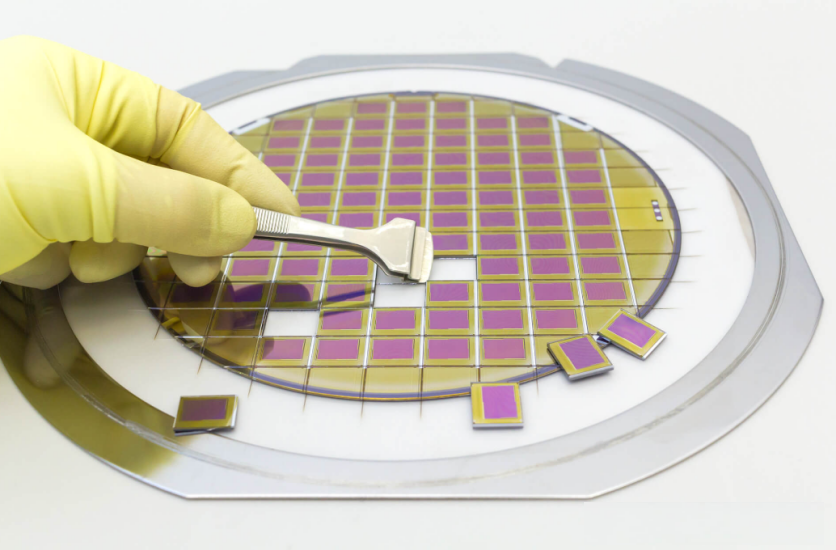

यह:वेफर के कट जाने के बाद, एकल चिप का वेफर बनता है, जिसे चिप बनने के लिए एक सीलबंद खोल जोड़ने की आवश्यकता होती है।

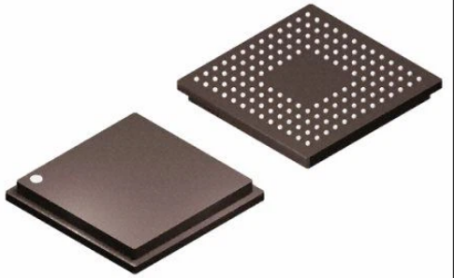

टुकड़ा:चिप का अंतिम पैकेज

उभार: बम्पिंग का तात्पर्य बम्पिंग पॉइंट से है। वेफर की सतह पर एक उत्तल बिंदु (सोना, टिन सीसा, सीसा रहित...आदि) उगाए जाने के बाद, (ज्यादातर फ्लिप प्रक्रिया पैकेज पर उपयोग किया जाता है, जो कि फ्लिपचिप है)।

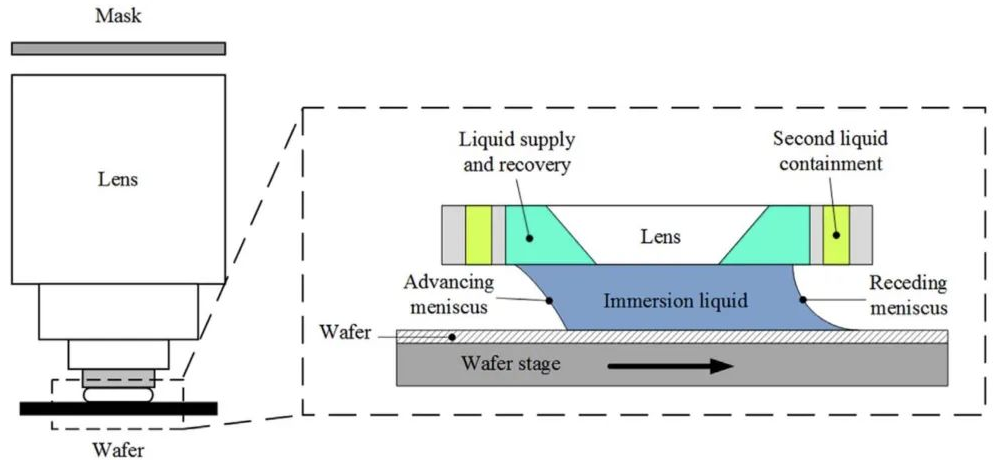

मास्क: वेफर पर चयनित क्षेत्र में एक अपारदर्शी ग्राफिक टेम्पलेट को मास्क करें, और बाद में क्षरण या प्रसार केवल चयनित क्षेत्र के बाहर के क्षेत्र को प्रभावित करेगा।

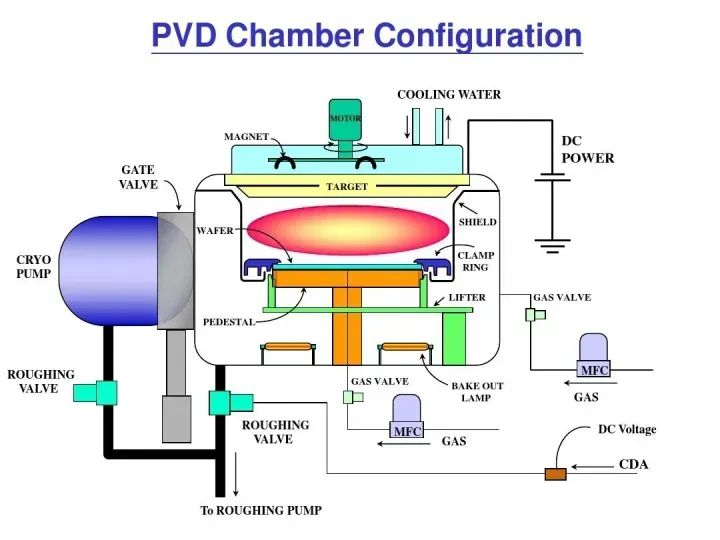

चैंबर: एक सीमित स्थान को संदर्भित करता है और इसका एक विशेष उद्देश्य होता है, जैसे वैक्यूमिंग, गैस प्रतिक्रिया या धातु स्पटरिंग।

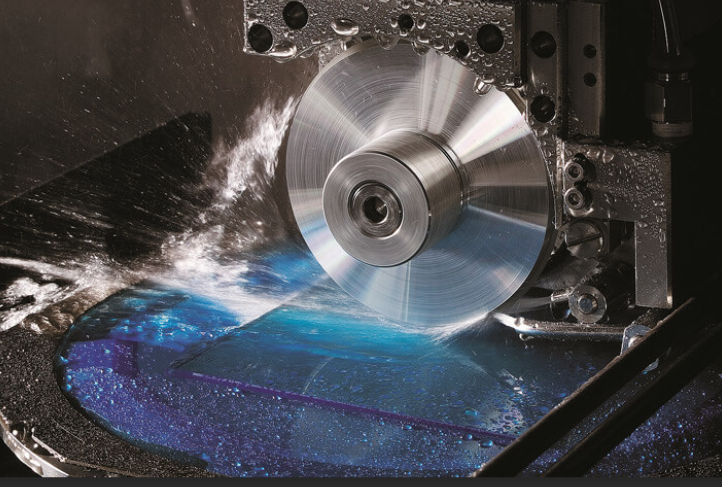

डाइसिंग वेफर: वेफरडाइसिंग, वेफर कटिंग

सीवीडी (रासायनिक वाष्प जमाव) : यह एक उन्नत तकनीक है जिसका व्यापक रूप से सामग्री तैयार करने के क्षेत्र में उपयोग किया जाता है, गैसों या गैस मिश्रण में रसायनों को ठोस सामग्री में परिवर्तित करने के लिए उच्च तापमान और कम दबाव वाले वातावरण का उपयोग किया जाता है।

पीवीडी (भौतिक वाष्प जमाव): आयन प्लाज्मा प्रौद्योगिकी द्वारा सब्सट्रेट की सतह पर किसी अन्य सामग्री को जोड़ने की एक विधि। स्प्रे, वाष्पीकरण...आदि का सामान्य नाम है।

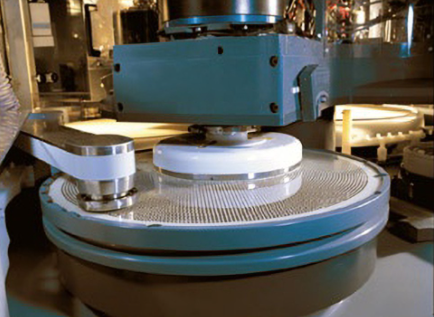

सीएमपी (केमिकल-मेचिनकल पोलिश): टीउन्होंने सतह पर पीसने वाले कणों से ढके ग्राइंडिंग पैड (पॉलिशिंगपैड) का उपयोग किया, रासायनिक योजक (अभिकर्मक) की सहायता से, रासायनिक प्रतिक्रिया और दोहरी प्रसंस्करण क्रिया के यांत्रिक पीस के साथ, असमान क्रिस्टल सतह पर इसकी सतह समतलता उपचार को पूरा करने के लिए .

सीडीए (स्वच्छ शुष्क वायु) : आमतौर पर 60 और 110psi के बीच दबाव वाली हवा को संदर्भित करता है, जिसे शुद्ध और सुखाया गया है। वायवीय घटकों के लिए गैस स्रोत के रूप में।

प्रसार: अर्धचालक उद्योग में, इसे अक्सर प्रीसेटिंग या आयन आरोपण द्वारा एक बहुत ही शुद्ध सिलिकॉन चिप पर प्रसार स्रोत के रूप में उपयोग किया जाता है, और भट्ठी ट्यूब में उच्च तापमान जोड़कर प्रसार कुछ घंटों के भीतर पूरा हो जाता है।

डीआई पानी: नल के पानी या भूजल, जिसमें बड़ी संख्या में बैक्टीरिया, धातु आयन और कण होते हैं, को उपकरण द्वारा निष्फल और शुद्ध किया जाना चाहिए, और फिर धातु आयनों की अशुद्धियों को हटा दिया जाता है, व्युत्पन्न पानी को "विआयनीकृत पानी" कहा जाता है। आईसी विनिर्माण के लिए डिज़ाइन किया गया।

डोपेंट: मूल अर्धचालक सामग्री में, इसके विद्युत गुणों को बदलने के लिए प्रसार द्वारा सक्रिय आरोपण या अन्य परमाणुओं या आयनों का समावेश।

डमी वेफर: एक सिलिकॉन वेफर जो प्रक्रिया में एक निश्चित सहायक भूमिका निभाता है, उत्पादों से अलग होता है। आम तौर पर, गुणवत्ता की आवश्यकताएं बहुत अधिक नहीं होती हैं।

डिज़ाइन

फैबलेस: फैब्रिकेशन और कम का एक संयोजन है, जो "कोई विनिर्माण व्यवसाय नहीं और केवल डिजाइन पर ध्यान केंद्रित" के साथ एकीकृत सर्किट डिजाइन के संचालन के एक तरीके को संदर्भित करता है। इसका उपयोग आईसी डिज़ाइन कंपनियों को संदर्भित करने के लिए भी किया जाता है जिनके पास चिप विनिर्माण संयंत्र नहीं है।

आरटीएल (रजिस्टर-ट्रांसफर लेवल): यह एक हार्डवेयर विवरण भाषा है जिसका उपयोग सिंक्रोनस डिजिटल सर्किट का वर्णन करने के लिए किया जाता है।

एसडीसी (सिनॉप्सिस डिज़ाइन चिप): डिज़ाइन बाधा फ़ाइल प्रदान करता है जिसे संश्लेषण उपकरण को आरटीएल को नेटलिस्ट में परिवर्तित करने की आवश्यकता होती है। एसडीसी के मुख्य विवरण में शामिल हैं: चिप ऑपरेटिंग आवृत्ति, चिप आईओ टाइमिंग, डिज़ाइन नियम, विशेष पथ, बिना जांच के पथ, इत्यादि।

चिप फ़ंक्शन सत्यापन: यह मुख्य रूप से चिप सत्यापन पद्धति को संदर्भित करता है, यह सत्यापित करता है कि आरटीएल और संदर्भ मॉडल सुसंगत हैं या नहीं।

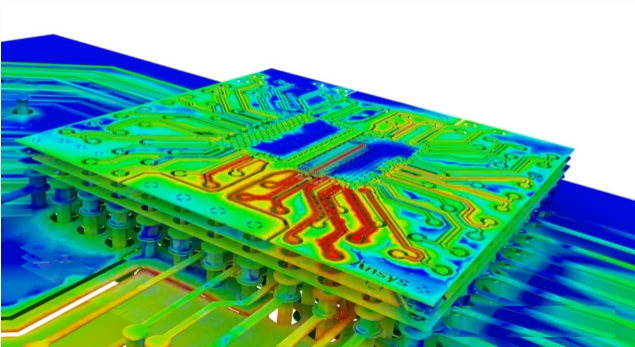

सिमुलेशन: सिमुलेशन आमतौर पर तरंग रूप में उत्पन्न होता है, सामान्य तौर पर, चिप फ़ंक्शन, सत्यापन, चिप बिजली की खपत, वास्तविक दृश्य के अधिक सहज प्रतिबिंब का अनुकरण किया जा सकता है।

आईपी (बौद्धिक संपदा): डिजाइन परिसंपत्तियां, कार्यात्मक सर्किट मॉड्यूल (कोर, इकाइयां) जिन्हें डिजाइन किया गया है

DesignRule: चूंकि सेमीकंडक्टर प्रक्रिया प्रौद्योगिकी एक पेशेवर, नाजुक और जटिल तकनीक है, जो विभिन्न विनिर्माण उपकरण प्रक्रिया विधियों (RECIPE) के प्रभाव के प्रति संवेदनशील है, इसलिए विनिर्माण प्रौद्योगिकी में संलग्न होने पर विचार करते समय तकनीकी प्रावधान करने के लिए विशिष्टताओं का एक सेट होना आवश्यक है। विभिन्न उत्पादों का पूर्णता और सफल निर्माण, जो "डिज़ाइननियम" है। इसे विभिन्न उत्पादों की आवश्यकताओं, विशिष्टताओं, विनिर्माण उपकरण और प्रक्रिया विधियों, प्रक्रिया क्षमताओं और संबंधित विद्युत मापदंडों के अनुसार तैयार किया गया है।

परीक्षा

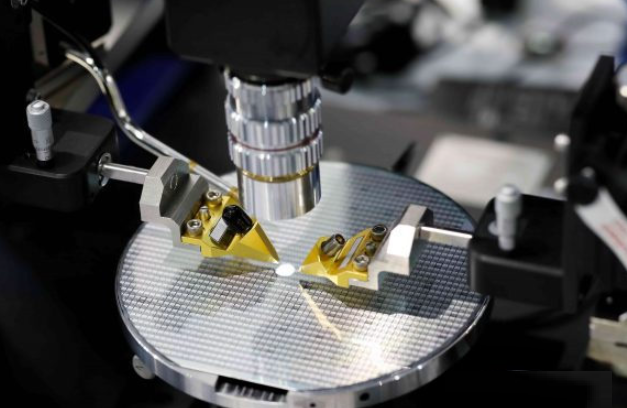

सीपी (चिप जांच): सीधे वेफर का परीक्षण करें, और परीक्षण वस्तु पूरे वेफर में प्रत्येक डाई के लिए है, इसका उद्देश्य यह सुनिश्चित करना है कि पूरे वेफर में प्रत्येक डाई मूल रूप से डिवाइस विशेषताओं या डिज़ाइन विनिर्देशों को पूरा कर सकती है, जिसमें आमतौर पर सत्यापन शामिल है वोल्टेज, करंट, टाइमिंग और फ़ंक्शन के लिए, इसका उपयोग फैब संयंत्रों में विनिर्माण प्रक्रिया के स्तर का परीक्षण करने के लिए किया जा सकता है।

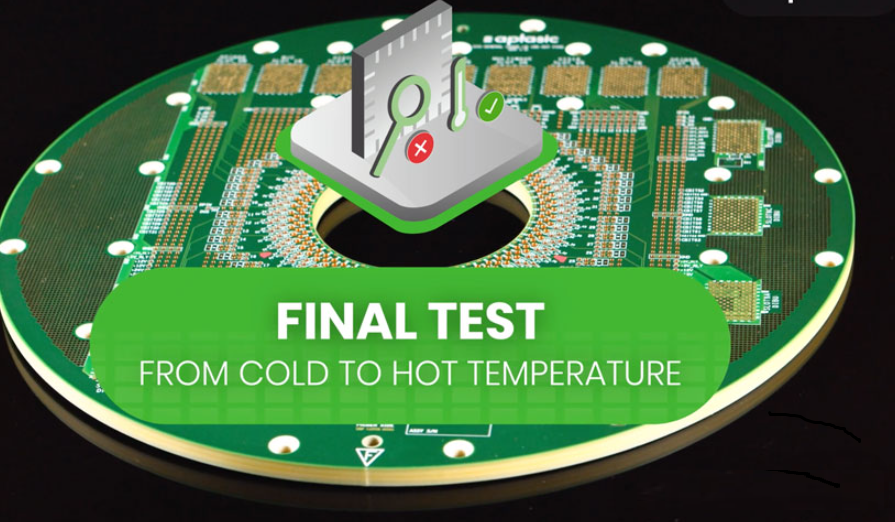

एफटी(अंतिम परीक्षण): चिप के कारखाने से निकलने से पहले यह आखिरी अवरोधन है। परीक्षण वस्तु एनकैप्सुलेटेड चिप के लिए है, जिसे सीपी परीक्षण के बाद एनकैप्सुलेट किया जाएगा और फिर एनकैप्सुलेशन के बाद एफटी परीक्षण किया जाएगा। इसका उपयोग पैकेजिंग प्लांट के तकनीकी स्तर का परीक्षण करने के लिए किया जा सकता है।

वेफर के लिए सीपी, यदि खराब डाई को पैकेजिंग करने की आवश्यकता नहीं है, तो पैकेजिंग की लागत और सब्सट्रेट लागत की बचत होती है।

सीपी परीक्षण पूरा होने के बाद, चिप विफलता को पैकेजिंग प्रक्रिया में पेश किया जाएगा, इसलिए विफल चिप को हटाने के लिए एफटी की भी आवश्यकता है।

उपज: चिप की उपज प्रक्रिया से संबंधित है, चिप की विफलता की एक निश्चित संभावना है, और चिप जितनी बड़ी होगी, विफलता की संभावना उतनी ही अधिक होगी।

आईपी (बौद्धिक संपदा):एकीकृत सर्किट डिजाइन में, एक विशिष्ट फ़ंक्शन के साथ सिद्ध और पुन: प्रयोज्य एकीकृत सर्किट का एक पूर्ण कार्यात्मक मॉड्यूल।

आईपी वर्गीकरण को लाइसेंस, वफादारी प्रति टोल संग्रह तरीके में विभाजित किया जा सकता है

लाइसेंस प्राधिकरण लाइसेंस: इस आईपी का उपयोग करने की अनुमति, आईपी का प्राधिकरण।

लॉयल्टी रॉयल्टी: उपयोगकर्ता द्वारा आईपी का उपयोग करने के बाद, उनसे प्रति चिप शुल्क लिया जाता है।

आईपी चिप का मुख्य घटक है, जैसे यूएसबी, पीसीआईई, सीपीयू आईपी हैं, पूरी चिप आईपी एकीकृत है, चिप अधिक जटिल काम कर सकती है, कोर आईपी का पुन: उपयोग है। उदाहरण के लिए, जो करोड़ों दरवाजे बनाते हैं, करोड़ों दरवाजे बनाते हैं, उनका आईपी पुन: उपयोग किया जा सकता है।

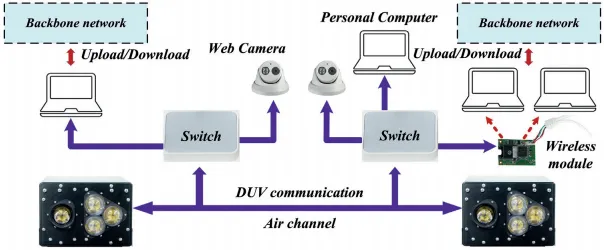

डीयूवी (गहरी पराबैंगनी किरणें) ईयूवी (चरम पराबैंगनी किरणें)

पैकेजिंग

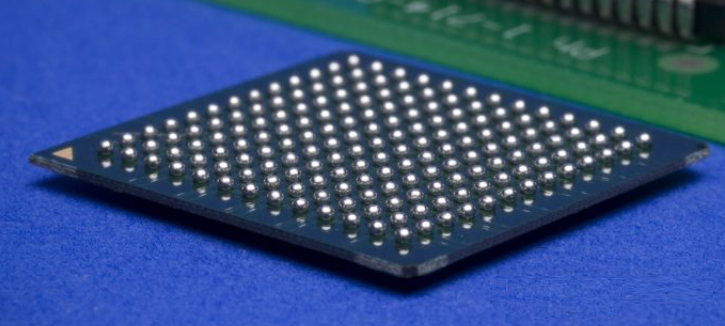

बीजीए (बॉल ग्रिड ऐरे): एक प्रकार का सतह पर लगा पैकेज जिसमें चिप माउंटेड सब्सट्रेट (बॉल ग्रिड ऐरे) पर कई कनेक्टेड सोल्डर बॉल्स व्यवस्थित होते हैं।

ASIC(एप्लिकेशन स्पेसिफिक इंटीग्रेटेड सर्किट): ASIC एक विशेष चिप है, जो एक चिप के लिए एक सामान्य शब्द है जिसे विशेष रूप से एक विशिष्ट आवश्यकता के लिए अनुकूलित किया जाता है। उदाहरण के लिए, समर्पित ऑडियो और वीडियो प्रोसेसर, और वर्तमान में, कई समर्पित एआई चिप उद्योग को एक प्रकार का ASIC माना जा सकता है।

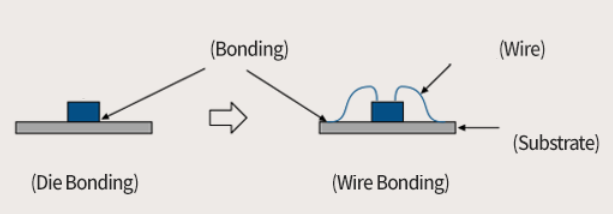

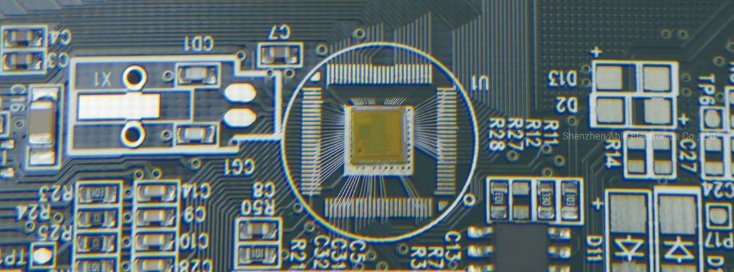

वायरबॉन्डिंग: वायर बॉन्डिंग (प्रेस वेल्डिंग, जिसे बाइंडिंग, बॉन्डिंग, वायर वेल्डिंग के रूप में भी जाना जाता है) धातु के तार (सोने के तार, एल्यूमीनियम तार ... आदि) के उपयोग को संदर्भित करता है, कनेक्शन को पूरा करने के लिए गर्म दबाव या अल्ट्रासोनिक ऊर्जा का उपयोग करता है। सॉलिड-स्टेट सर्किट की आंतरिक वायरिंग, यानी चिप और सर्किट या लीड फ्रेम के बीच का कनेक्शन।

मरो बाध्य:

फ्लिपचिप: एक टिन लेड बॉल को आई/ओपैड पर जमा किया जाता है, और फिर चिप को पलट दिया जाता है और सिरेमिक सब्सट्रेट के साथ पिघले हुए टिन लेड बॉल का उपयोग करके गर्म किया जाता है।

सीओबी (चिप-ऑन-बोर्ड): ऑन-बोर्ड चिप पैकेजिंग में नंगे चिप को प्रवाहकीय या गैर-प्रवाहकीय चिपकने वाले के साथ पीसीबी से जोड़ना है, और फिर इसके विद्युत कनेक्शन को प्राप्त करने के लिए लीड बॉन्डिंग करना है, और चिप और बॉन्ड लीड को लपेटना है चिपकने वाला.

एसओसी (सिस्टम ऑन चिप): सीपीयू, बस, पेरिफेरल्स...आदि को चिप के आंतरिक कार्यान्वयन में डालना है। उदाहरण के लिए, एक मोबाइल फ़ोन प्रोसेसर एक जटिल SOC चिप है।

एसआईपी (पैकेज में सिस्टम): SiP पैकेज सीपीयू, जीपीयू, मेमोरी...आदि सहित विभिन्न कार्यों के साथ कच्ची चिप है। एक पैकेज बॉडी में एकीकृत किया गया है, ताकि एक संपूर्ण चिप प्रणाली प्राप्त की जा सके।

एसओपी(छोटी रूपरेखा पैकेज):आईसी पैकेजों का एक छोटा बाहरी पैकेज जिसमें लीड दोनों दिशाओं में खींचे जाते हैं

डीएएफ (डाई अटैच फिल्म): वेफर बॉन्डिंग फिल्म बॉन्डिंग तकनीक

सीएमओएस (पूरक धातु ऑक्साइड सेमीकंडक्टर): पूरक धातु ऑक्साइड सेमीकंडक्टर। यह बड़े पैमाने पर एकीकृत सर्किट चिप्स या इस तकनीक का उपयोग करके बनाए गए चिप्स बनाने के लिए उपयोग की जाने वाली तकनीक को संदर्भित करता है, जो रैम चिप का एक टुकड़ा है जिसे कंप्यूटर मदरबोर्ड पर पढ़ा और लिखा जा सकता है। पढ़ने-लिखने की विशेषताओं के कारण, इसका उपयोग कंप्यूटर मदरबोर्ड पर कंप्यूटर हार्डवेयर पैरामीटर सेट होने के बाद BIOS डेटा को सहेजने के लिए किया जाता है, और इस चिप का उपयोग केवल डेटा संग्रहीत करने के लिए किया जाता है।

JEDEC (संयुक्त इलेक्ट्रॉन डिवाइस इंजीनियरिंग परिषद मानक): पैकेज आयाम के लिए अमेरिकी मानक विनिर्देश।

फाउंटिल टेक्नोलॉजीज पीटीई लिमिटेड, सेमीकंडक्टर विनिर्माण उद्योग पर ध्यान केंद्रित कर रहा है, मुख्य उत्पादों में शामिल हैं: पिन चक, छिद्रपूर्ण सिरेमिक चक, सिरेमिक अंत प्रभावक, सिरेमिक स्क्वायर बीम, सिरेमिक स्पिंडल, संपर्क और बातचीत के लिए आपका स्वागत है!