चिप पैकेज ताप अपव्यय समस्या को कैसे हल करें

उन्नत पैकेजिंग चिप्स न केवल उच्च-प्रदर्शन कंप्यूटिंग, कृत्रिम बुद्धिमत्ता, शक्ति घनत्व वृद्धि आदि की जरूरतों को पूरा कर सकते हैं, बल्कि उन्नत पैकेजिंग की गर्मी अपव्यय समस्या भी जटिल हो गई है। क्योंकि एक चिप पर हॉट स्पॉट पड़ोसी चिप्स के ताप वितरण को प्रभावित करते हैं। SoCs की तुलना में मॉड्यूल में चिप्स के बीच अंतर्संबंध भी धीमे होते हैं।

सीमेंस डिजिटल इंडस्ट्री सॉफ्टवेयर में इलेक्ट्रॉनिक्स और सेमीकंडक्टर के उद्योग प्रमुख जॉन पैरी ने कहा: "दुनिया के मल्टी-कोर जैसे क्षेत्रों में जाने से पहले, आप एक चिप के साथ काम कर रहे थे जिसकी अधिकतम शक्ति लगभग 150 वाट प्रति वर्ग सेंटीमीटर थी, जो कि थी एक एकल बिंदु ताप स्रोत। आप तीनों दिशाओं में गर्मी को नष्ट कर सकते हैं, जिससे आप कुछ उच्च शक्ति घनत्व प्राप्त कर सकते हैं, लेकिन जब आपके पास एक चिप होती है, तो उसके बगल में एक और चिप रखें, और फिर उसके बगल में एक और चिप रखें, वे गर्म हो जाते हैं एक दूसरे के ऊपर। इसका मतलब है कि आप प्रत्येक चिप में समान शक्ति स्तर को बर्दाश्त नहीं कर सकते हैं, जो थर्मल चुनौती को और अधिक कठिन बना देता है।"

यह मुख्य कारणों में से एक है कि 3डी-आईसी स्टैकिंग बाजार में धीमी प्रगति कर रही है। जबकि अवधारणा शक्ति दक्षता और एकीकरण के दृष्टिकोण से समझ में आती है - और 3डी नंद और एचबीएम में अच्छी तरह से काम करती है - जब तर्क शामिल होता है तो यह एक अलग कहानी है। लॉजिक चिप गर्मी उत्पन्न करती है, और लॉजिक जितना सघन होगा, प्रसंस्करण तत्वों का उपयोग उतना ही अधिक होगा, गर्मी उतनी ही अधिक होगी। यह तार्किक स्टैकिंग को दुर्लभ बनाता है।

सही पैकेज चुनें

चिप डिजाइनरों के लिए, पैकेज करने के कई तरीके हैं। लेकिन चिप एकीकरण का प्रदर्शन महत्वपूर्ण है। सिलिकॉन, टीएसवी और कॉपर कॉलम जैसे सभी घटकों में थर्मल विस्तार (टीसीई) का अलग-अलग गुणांक होता है, जो असेंबली उपज और दीर्घकालिक विश्वसनीयता को प्रभावित करता है।

सीपीयू और एचबीएम के साथ वर्तमान लोकप्रिय फ्लिप बीजीए पैकेज का क्षेत्रफल लगभग 2500 वर्ग मिलीमीटर है। ओन्टो इनोवेशन में सॉफ्टवेयर उत्पाद प्रबंधन के प्रमुख माइक मैकइंटायर ने कहा: "हम देख रहे हैं कि एक बड़ी चिप संभावित रूप से चार या पांच छोटी चिप्स बन सकती है। इसलिए इन चिप्स को एक-दूसरे से बात करने के लिए आपके पास अधिक I/O होना चाहिए। तो आप गर्मी वितरित कर सकते हैं अंततः, गर्मी अपव्यय एक समस्या है जिसे केवल सिस्टम स्तर पर निपटाया जा सकता है, और यह व्यापार-बंद की एक श्रृंखला के साथ आता है।

वास्तव में, कुछ उपकरण इतने जटिल होते हैं कि विशिष्ट क्षेत्रों में अनुप्रयोगों के लिए इन उपकरणों को अनुकूलित करने के लिए घटकों को आसानी से बदलना मुश्किल होता है। यही कारण है कि कई उन्नत पैकेजिंग उत्पाद सर्वर चिप्स जैसे बहुत अधिक मात्रा या मूल्य-लोचदार घटकों के लिए होते हैं।

चिप मॉड्यूल सिमुलेशन और परीक्षण में प्रगति

फिर भी, इंजीनियर पैकेज्ड मॉड्यूल के निर्माण से पहले पैकेज विश्वसनीयता का थर्मल विश्लेषण करने के नए तरीकों की तलाश कर रहे हैं। उदाहरण के लिए, सीमेंस एक दोहरे ASIC आधारित मॉड्यूल का उदाहरण प्रदान करता है जो BGA पैकेज में एक बहुपरत कार्बनिक सब्सट्रेट पर एक फैन-आउट पुनर्वितरण परत (RDL) स्थापित करता है। यह दो मॉडलों का उपयोग करता है, एक आरडीएल-आधारित डब्ल्यूएलपी के लिए और दूसरा मल्टी-लेयर ऑर्गेनिक सब्सट्रेट बीजीए के लिए। ये पैकेजिंग मॉडल मानकीकृत हैं, ईडीए जानकारी पेश करने से पहले सब्सट्रेट स्टैकिंग और बीजीए शामिल हैं, और प्रारंभिक सामग्री मूल्यांकन और चिप प्लेसमेंट चयन को सक्षम करते हैं। इसके बाद, ईडीए डेटा आयात किया जाता है, और प्रत्येक मॉडल के लिए, सामग्री मानचित्र सभी परतों में तांबे के वितरण का विस्तृत थर्मल विवरण प्रदान करने में सक्षम है।

जेसीईटी में तकनीकी विपणन निदेशक एरिक ओयांग ने जेसीईटी और मेटा के इंजीनियरों के साथ मिलकर सिंगल-चिप, मल्टी-चिप मॉड्यूल, 2.5डी प्लगबोर्ड और 3डी स्टैक्ड चिप्स के थर्मल प्रदर्शन की तुलना एक एएसआईसी और दो स्राम के साथ की। [1] ऐप्पल-टू-एप्पल तुलना सर्वर वातावरण, वैक्यूम चैम्बर के साथ रेडिएटर और टीआईएम को अपरिवर्तित छोड़ देती है। गर्मी के मामले में, 2.5D और MCM 3D या सिंगल-चिप चिप्स से बेहतर प्रदर्शन करते हैं।

परिमाणित थर्मल प्रतिरोध

हम यह समझ सकते हैं कि तापमान और प्रतिरोध मूल्यों को ट्रैक करने के लिए तापमान अंतर और पावर फ़ंक्शन की मानक विधि का उपयोग करते हुए सिलिकॉन चिप्स, सर्किट बोर्ड, गोंद, टीआईएम या पैकेजिंग कैप के माध्यम से गर्मी का संचालन कैसे किया जाता है।

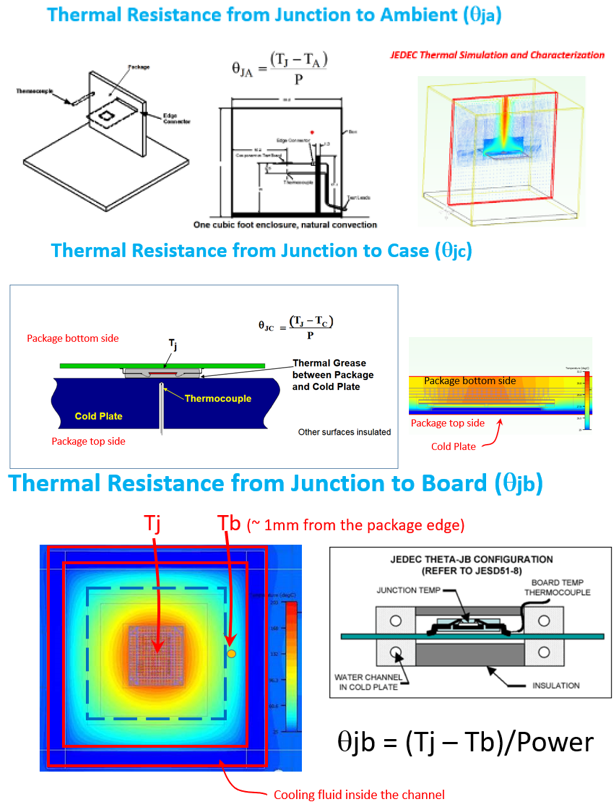

"थर्मल पथ को तीन प्रमुख मानों द्वारा निर्धारित किया जाता है - डिवाइस नोड से पर्यावरण तक थर्मल प्रतिरोध, नोड से आवास तक थर्मल प्रतिरोध [पैकेज के शीर्ष पर], और नोड से बोर्ड तक थर्मल प्रतिरोध , "जेसीईटी के ओयांग कहते हैं। वह बताते हैं कि कम से कम, जेसीईटी के ग्राहकों को ɵja, ɵjc और ɵjb की आवश्यकता होती है, जिनका वे सिस्टम डिज़ाइन में उपयोग करते हैं। उन्हें आवश्यकता हो सकती है कि दिया गया थर्मल प्रतिरोध एक विशिष्ट मूल्य से अधिक न हो और पैकेज डिज़ाइन वह प्रदर्शन प्रदान करे।

थर्मल सिमुलेशन सामग्रियों के चयन और संयोजन का पता लगाने का सबसे किफायती तरीका है। कार्यशील अवस्था में चिप के अनुकरण के माध्यम से, हम आमतौर पर एक या अधिक हॉट स्पॉट पाते हैं, इसलिए हम गर्मी अपव्यय की सुविधा के लिए हॉट स्पॉट के नीचे सब्सट्रेट में तांबा जोड़ सकते हैं; या पैकेजिंग सामग्री बदलें, रेडिएटर बढ़ाएं। सिस्टम इंटीग्रेटर निर्दिष्ट कर सकता है कि थर्मल प्रतिरोध ɵja, ɵjc, और ɵjb कुछ मूल्यों से अधिक नहीं होना चाहिए। सामान्य परिस्थितियों में, सिलिकॉन जंक्शन तापमान 125 डिग्री सेल्सियस से नीचे रखा जाना चाहिए। सिमुलेशन पूरा होने के बाद, पैकेजिंग प्लांट अंतिम पैकेज योजना पर पहुंचने के लिए प्रयोगों का एक डिजाइन (डीओई) आयोजित करता है।

टीआईएम चुनें

पैकेज में, 90% से अधिक गर्मी पैकेज के माध्यम से चिप के शीर्ष से रेडिएटर तक फैल जाती है, जो आमतौर पर एनोडाइज्ड एल्यूमीनियम पर आधारित एक ऊर्ध्वाधर पंख होता है। उच्च तापीय चालकता वाली थर्मल इंटरफ़ेस सामग्री (टीआईएम) को गर्मी हस्तांतरण में मदद के लिए चिप और पैकेज के बीच रखा जाता है। सीपीयू के लिए अगली पीढ़ी के टीआईएम में क्रमशः इंडियम और टिन जैसे शीट धातु मिश्र धातु, साथ ही 60W/mK और 50W/mK की चालकता के साथ सिल्वर-सिंटेड टिन शामिल हैं। जैसे-जैसे विक्रेता SoCs को चिपलेट प्रक्रियाओं में परिवर्तित करते हैं, विभिन्न गुणों और मोटाई वाले अधिक TIM की आवश्यकता होती है।

एमकोर में अनुसंधान और विकास के वरिष्ठ निदेशक यंगडो क्वोन ने कहा कि उच्च-घनत्व प्रणालियों के लिए, चिप और पैकेज के बीच टीआईएम का थर्मल प्रतिरोध पैक किए गए मॉड्यूल के समग्र थर्मल प्रतिरोध पर अधिक प्रभाव डालता है। बिजली के रुझान नाटकीय रूप से बढ़ रहे हैं, खासकर तर्क के लिए, इसलिए हम विश्वसनीय अर्धचालक संचालन सुनिश्चित करने के लिए जंक्शन तापमान को कम रखने पर ध्यान केंद्रित करते हैं। जबकि टीआईएम आपूर्तिकर्ता अपनी सामग्रियों के लिए थर्मल प्रतिरोध मान प्रदान करते हैं, वास्तव में, चिप से पैकेज (ɵjc) तक थर्मल प्रतिरोध असेंबली प्रक्रिया से ही प्रभावित होता है, जिसमें चिप और टीआईएम के बीच संबंध गुणवत्ता और संपर्क क्षेत्र भी शामिल है। उन्होंने नोट किया कि नियंत्रित वातावरण में वास्तविक असेंबली टूल और बॉन्डिंग सामग्री के साथ परीक्षण करना वास्तविक थर्मल गुणों को समझने और ग्राहक सत्यापन के लिए सर्वोत्तम टीआईएम का चयन करने के लिए महत्वपूर्ण है।

विभिन्न तरीकों से गर्मी से निपटने के लिए

चिप निर्माता गर्मी अपव्यय समस्या को हल करने के तरीके तलाश रहे हैं। कीसाइट टेक्नोलॉजीज में मेमोरी सॉल्यूशंस के प्रोग्राम मैनेजर रैंडी व्हाइट ने कहा: "पैकेज समान है, यदि आप चिप आकार क्षेत्र को एक चौथाई तक कम करते हैं, तो यह तेज हो जाएगा। इसके परिणामस्वरूप कुछ सिग्नल अखंडता अंतर हो सकते हैं। क्योंकि बॉन्डिंग लाइन बाहरी पैकेज चिप में प्रवेश करेगा, लाइन जितनी लंबी होगी, इंडक्शन उतना ही अधिक होगा, इसलिए एक विद्युत प्रदर्शन भाग होता है तो आप एक छोटी सी जगह में इतनी अधिक ऊर्जा का उपभोग कैसे करते हैं? यह एक और महत्वपूर्ण पैरामीटर है जिसकी आवश्यकता है अध्ययन किया।" इससे अत्याधुनिक बॉन्डिंग अनुसंधान में महत्वपूर्ण निवेश हुआ है जो हाइब्रिड बॉन्डिंग पर ध्यान केंद्रित करता है। लेकिन हाइब्रिड बॉन्डिंग की लागत अधिक है, और यह अभी भी उच्च-प्रदर्शन प्रोसेसर-प्रकार के अनुप्रयोगों तक ही सीमित है, टीएसएमसी वर्तमान में इस तकनीक की पेशकश करने वाली एकमात्र कंपनियों में से एक है। हालाँकि, सीएमओएस चिप्स या सिलिकॉन-आधारित गैलियम नाइट्राइड पर फोटॉन के संयोजन की संभावना बहुत आशाजनक है।

फाउंटिल टेक्नोलॉजीज पीटीई लिमिटेड, सेमीकंडक्टर विनिर्माण उद्योग पर ध्यान केंद्रित कर रहा है, मुख्य उत्पादों में शामिल हैं: पिन चक, छिद्रपूर्ण सिरेमिक चक, सिरेमिक अंत प्रभावक, सिरेमिक स्क्वायर बीम, सिरेमिक स्पिंडल, संपर्क और बातचीत के लिए आपका स्वागत है!