Come risolvere il problema della dissipazione del calore del pacchetto chip

I chip di imballaggio avanzati non solo possono soddisfare le esigenze del calcolo ad alte prestazioni, dell'intelligenza artificiale, della crescita della densità di potenza, ecc., ma anche il problema della dissipazione del calore degli imballaggi avanzati è diventato complicato. Perché i punti caldi su un chip influenzano la distribuzione del calore dei chip vicini. Anche le interconnessioni tra i chip sono più lente nei moduli che nei SoC.

John Parry, responsabile del settore elettronica e semiconduttori presso Siemens Digital Industry Software, ha dichiarato: "Prima che il mondo si spostasse in settori come il multi-core, avevi a che fare con un chip che aveva una potenza massima di circa 150 watt per centimetro quadrato, che era una fonte di calore a punto singolo. Puoi dissipare il calore in tutte e tre le direzioni, così puoi ottenere densità di potenza piuttosto elevate. Ma quando hai un chip, metti un altro chip accanto ad esso, e poi metti un altro chip accanto ad esso, si riscaldano l'uno con l'altro. Ciò significa che non è possibile tollerare che ogni chip abbia lo stesso livello di potenza, il che rende la sfida termica molto più difficile."

Questo è uno dei motivi principali per cui lo stacking 3D-IC sta facendo lenti progressi nel mercato. Sebbene il concetto abbia senso dal punto di vista dell'efficienza energetica e dell'integrazione - e funzioni bene in 3D NAND e HBM - la storia è diversa quando viene inclusa la logica. Il chip logico genera calore e quanto più densa è la logica, tanto maggiore è l'utilizzo degli elementi di elaborazione, tanto maggiore è il calore. Ciò rende raro l'impilamento logico.

Scegli il pacchetto giusto

Per i progettisti di chip, ci sono molti modi per confezionare. Ma le prestazioni dell’integrazione dei chip sono cruciali. Componenti come colonne in silicio, TSV e rame hanno tutti un diverso coefficiente di espansione termica (TCE), che influisce sulla resa dell'assemblaggio e sull'affidabilità a lungo termine.

L'attuale popolare pacchetto BGA Flip con CPU e HBM ha un'area di circa 2500 millimetri quadrati. Mike McIntyre, responsabile della gestione dei prodotti software presso Onto Innovation, ha dichiarato: "Stiamo vedendo un grande chip potenzialmente diventare quattro o cinque piccoli chip. Quindi è necessario avere più I/O affinché questi chip possano comunicare tra loro. Quindi puoi distribuire il calore In definitiva, la dissipazione del calore è un problema che può essere risolto solo a livello di sistema e comporta una serie di compromessi.

Alcuni dispositivi, infatti, sono così complessi che è difficile sostituire facilmente i componenti per personalizzare questi dispositivi per applicazioni in campi specifici. Questo è il motivo per cui molti prodotti di imballaggio avanzati sono destinati a componenti con volumi molto elevati o elastici in termini di prezzo, come i chip per server.

Progressi nella simulazione e nei test dei moduli chip

Tuttavia, gli ingegneri sono alla ricerca di nuovi modi per eseguire l'analisi termica dell'affidabilità del pacchetto prima che i moduli confezionati vengano fabbricati. Ad esempio, Siemens fornisce un esempio di un modulo doppio basato su ASIC che installa uno strato di ridistribuzione fan-out (RDL) su un substrato organico multistrato in un pacchetto BGA. Utilizza due modelli, uno per il WLP basato su RDL e l'altro per il substrato organico multistrato BGA. Questi modelli di packaging sono parametrizzati, includono l'impilamento dei substrati e il BGA prima che vengano introdotte le informazioni EDA e consentono la valutazione anticipata del materiale e la selezione del posizionamento dei chip. Successivamente, vengono importati i dati EDA e, per ciascun modello, la mappa del materiale è in grado di fornire una descrizione termica dettagliata della distribuzione del rame in tutti gli strati.

Eric Ouyang, Direttore del marketing tecnico di JCET, insieme agli ingegneri di JCET e Meta, ha confrontato le prestazioni termiche di moduli a chip singolo e multi-chip, schede plugboard 2.5D e chip impilati 3D con un ASIC e due Sram. [1] Il confronto Apple-Apple lascia invariati l'ambiente server, il radiatore con camera a vuoto e TIM. In termini di calore, 2.5D e MCM hanno prestazioni migliori rispetto ai chip 3D o a chip singolo.

Resistenza termica quantizzata

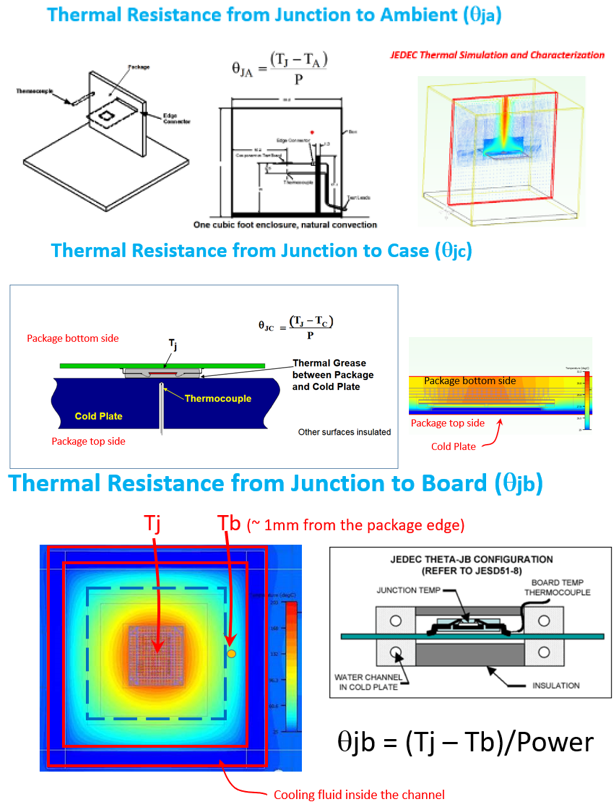

Possiamo capire come viene condotto il calore attraverso chip di silicio, circuiti stampati, colle, TIM o cappucci di imballaggio, utilizzando il metodo standard della differenza di temperatura e la funzione di potenza per monitorare i valori di temperatura e resistenza.

"Il percorso termico è quantificato da tre valori chiave: la resistenza termica dal nodo del dispositivo all'ambiente, la resistenza termica dal nodo all'alloggiamento [nella parte superiore del pacchetto] e la resistenza termica dal nodo alla scheda ", afferma Ouyang del JCET. Come minimo, sottolinea, i clienti di JCET hanno bisogno di ɵja, ɵjc e ɵjb, che poi utilizzano nella progettazione del sistema. Potrebbero richiedere che una determinata resistenza termica non superi un valore specifico e che il design del pacchetto fornisca tale prestazione.

La simulazione termica è il modo più economico per esplorare la selezione e la collocazione dei materiali. Attraverso la simulazione del chip nello stato di funzionamento, solitamente troviamo uno o più punti caldi, quindi possiamo aggiungere rame al substrato sotto il punto caldo per facilitare la dissipazione del calore; Oppure cambia il materiale di imballaggio, aumenta il radiatore. L'integratore del sistema può specificare che la resistenza termica ɵja, ɵjc e ɵjb non deve superare determinati valori. In circostanze normali, la temperatura della giunzione del silicio dovrebbe essere mantenuta al di sotto di 125 °C. Al termine della simulazione, l'impianto di confezionamento conduce un disegno di esperimenti (DOE) per arrivare al piano di confezionamento finale.

Seleziona TIM

Nel package, oltre il 90% del calore viene dissipato dalla parte superiore del chip al radiatore, che solitamente è un'aletta verticale in alluminio anodizzato. I materiali di interfaccia termica (TIM) con elevata conduttività termica vengono posizionati tra il chip e il package per favorire il trasferimento del calore. I TIM di prossima generazione per CPU includono leghe metalliche come indio e stagno, nonché stagno sinterizzato con argento con conduttività rispettivamente di 60 W/mK e 50 W/mK. Man mano che i fornitori passano dai SoC ai processi chiplet, sono necessari più TIM con proprietà e spessori diversi.

YoungDo Kweon, direttore senior della ricerca e sviluppo di Amkor, ha affermato che per i sistemi ad alta densità, la resistenza termica del TIM tra il chip e il package ha un impatto maggiore sulla resistenza termica complessiva del modulo confezionato. Le tendenze di potenza stanno aumentando notevolmente, soprattutto per la logica, quindi ci concentriamo sul mantenimento della temperatura di giunzione bassa per garantire un funzionamento affidabile dei semiconduttori. Mentre i fornitori TIM forniscono valori di resistenza termica per i loro materiali, in realtà la resistenza termica dal chip al package (ɵjc) è influenzata dal processo di assemblaggio stesso, compresa la qualità del legame e l’area di contatto tra chip e TIM. Sottolinea che i test con strumenti di assemblaggio e materiali di incollaggio reali in un ambiente controllato sono fondamentali per comprendere le proprietà termiche effettive e selezionare il miglior TIM per la verifica del cliente.

Affrontare il caldo in modi diversi

I produttori di chip sono alla ricerca di modi per risolvere il problema della dissipazione del calore. Randy White, program manager per le soluzioni di memoria presso Keysight Technologies, ha dichiarato: "Il pacchetto è lo stesso, se si riduce l'area delle dimensioni del chip di un quarto, aumenterà la velocità. Ciò potrebbe comportare alcune differenze nell'integrità del segnale. Perché la linea di collegamento del pacchetto esterno entrerà nel chip, più lunga è la linea, maggiore è l'induttanza, quindi c'è una parte relativa alle prestazioni elettriche. Quindi, come si consuma così tanta energia in uno spazio sufficientemente piccolo? Questo è un altro parametro chiave che deve essere presente studiato." Ciò ha portato a investimenti significativi nella ricerca sui bonding all’avanguardia che sembra concentrarsi sui bond ibridi. Ma il costo del bonding ibrido è elevato ed è ancora limitato alle applicazioni di tipo processore ad alte prestazioni, poiché TSMC è una delle poche aziende attualmente a offrire questa tecnologia. Tuttavia, la prospettiva di combinare fotoni su chip CMOS o nitruro di gallio a base di silicio è molto promettente.

Fountyl Technologies PTE Ltd, si concentra sull'industria manifatturiera dei semiconduttori, i prodotti principali includono: mandrino a perno, mandrino in ceramica porosa, effettore finale in ceramica, trave quadrata in ceramica, mandrino in ceramica, benvenuto per contatto e negoziazione!