チップパッケージの放熱問題を解決する方法

高度なパッケージング チップは、高性能コンピューティング、人工知能、電力密度の増大などのニーズを満たすことができるだけでなく、高度なパッケージングの放熱問題も複雑になっています。 1 つのチップ上のホット スポットが隣接するチップの熱分布に影響を与えるためです。 チップ間の相互接続も、SoC よりもモジュールの方が遅くなります。

シーメンス デジタル インダストリー ソフトウェアのエレクトロニクスおよび半導体業界責任者であるジョン パリー氏は、「世界がマルチコアなどの分野に移行する前は、最大電力が 1 平方センチメートルあたり約 150 ワットのチップを扱っていました。単一点熱源では 3 方向すべてに熱を放散できるため、かなり高い電力密度を達成できます。しかし、チップをその隣に置き、さらにその隣に別のチップを置くと、熱が発生します。つまり、各チップが同じ電力レベルを持つことを許容できず、熱の問題がさらに難しくなります。」

これが、市場で 3D-IC スタッキングの進歩が遅い主な理由の 1 つです。 この概念は電力効率と統合の観点からは理にかなっていますが、3D NAND や HBM ではうまく機能しますが、ロジックが含まれる場合は話が異なります。 ロジック チップは熱を発生します。ロジックの密度が高くなるほど、処理要素の使用率が高くなるほど、熱も大きくなります。 これにより、論理的なスタッキングがまれになります。

適切なパッケージを選択してください

チップ設計者にとって、パッケージ化にはさまざまな方法があります。 ただし、チップ統合のパフォーマンスは非常に重要です。 シリコン、TSV、銅カラムなどのコンポーネントはすべて異なる熱膨張係数 (TCE) を持っており、これがアセンブリの歩留まりや長期信頼性に影響します。

CPU と HBM を備えた現在人気のあるフリップ BGA パッケージの面積は約 2500 平方ミリメートルです。 Onto Innovation のソフトウェア製品管理責任者、Mike McIntyre 氏は次のように述べています。「大きなチップが 4 つまたは 5 つの小さなチップになる可能性があります。したがって、これらのチップが相互に通信するには、より多くの I/O が必要になります。したがって、熱を分散させることができます。最終的に、熱放散はシステム レベルでのみ対処できる問題であり、一連のトレードオフが伴います。

実際、一部のデバイスは非常に複雑であるため、特定の分野のアプリケーションに合わせてこれらのデバイスをカスタマイズするためにコンポーネントを簡単に交換することが困難です。 このため、多くの高度なパッケージング製品は、サーバー チップなどの非常に大量生産または価格に依存するコンポーネント向けです。

チップモジュールのシミュレーションとテストの進歩

それにもかかわらず、エンジニアは、パッケージ化されたモジュールを製造する前にパッケージの信頼性の熱解析を実行する新しい方法を探しています。 たとえば、シーメンスは、BGA パッケージの多層有機基板上にファンアウト再配線層 (RDL) をインストールするデュアル ASIC ベースのモジュールの例を提供しています。 RDL ベースの WLP 用と多層有機基板 BGA 用の 2 つのモデルを使用します。 これらのパッケージング モデルはパラメータ化されており、EDA 情報が導入される前に基板スタッキングと BGA が含まれており、早期の材料評価とチップ配置の選択が可能になります。 次に、EDA データがインポートされ、各モデルの材料マップにより、すべての層の銅分布の詳細な熱的記述が提供されます。

JCET のテクニカル マーケティング ディレクターである Eric Ouyang 氏は、JCET および Meta のエンジニアとともに、1 つの ASIC と 2 つの Sram を備えたシングルチップ、マルチチップ モジュール、2.5D プラグボード、および 3D スタック チップの熱性能を比較しました。 [1] Apple 間の比較では、サーバー環境、真空チャンバー付きラジエーター、および TIM は変更されません。 熱の点では、2.5D と MCM は 3D またはシングルチップ チップよりもパフォーマンスが優れています。

量子化された熱抵抗

温度差と電力関数の標準的な方法を使用して温度と抵抗値を追跡しながら、シリコンチップ、回路基板、接着剤、TIM、パッケージングキャップを介して熱がどのように伝導するかを理解できます。

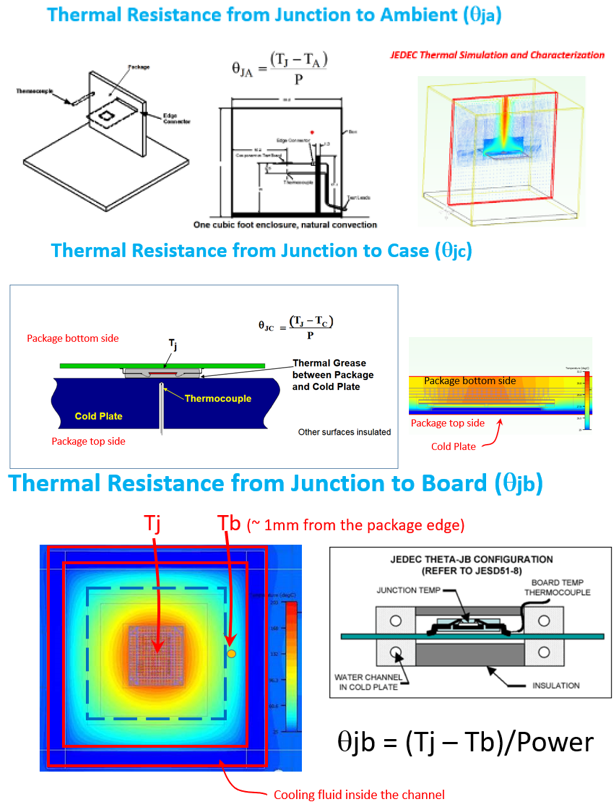

「熱経路は 3 つの主要な値によって定量化されます。デバイス ノードから環境までの熱抵抗、ノードからハウジング (パッケージ上部) までの熱抵抗、ノードからボードまでの熱抵抗です。 」と JCET の欧陽氏は言います。 少なくとも、JCET の顧客は ɵja、ɵjc、および ɵjb を必要とし、これらをシステム設計で使用すると彼は指摘します。 特定の熱抵抗が特定の値を超えないこと、およびパッケージ設計がその性能を提供することを要求する場合があります。

熱シミュレーションは、材料の選択と配置を検討するための最も経済的な方法です。 動作状態のチップのシミュレーションを通じて、通常、1 つ以上のホット スポットが見つかるため、熱放散を促進するためにホット スポットの下の基板に銅を追加できます。 または、梱包材を変更したり、ラジエーターを増やしたりします。 システム インテグレータは、熱抵抗 ɵja、ɵjc、および ɵjb が特定の値を超えてはならないと指定する場合があります。 通常の状況では、シリコン ジャンクション温度は 125 °C 未満に保つ必要があります。シミュレーションが完了すると、パッケージング プラントは実験計画法 (DOE) を実施して、最終的なパッケージ計画に到達します。

TIMを選択します

パッケージ内では、熱の 90% 以上がパッケージを介してチップの上部からラジエーターまで放散されます。ラジエーターは通常、陽極酸化アルミニウムをベースとした垂直フィンです。 熱伝導率の高いサーマル・インターフェース・マテリアル(TIM)がチップとパッケージの間に配置され、熱の伝達を助けます。 CPU 用の次世代 TIM には、インジウムやスズなどのシートメタル合金と、それぞれ 60W/mK と 50W/mK の導電率を持つ銀焼結スズが含まれます。 ベンダーが SoC をチップレット プロセスに移行するにつれて、さまざまな特性と厚さを備えたより多くの TIM が必要になります。

Amkorの研究開発シニアディレクターであるYoungDo Kweon氏は、高密度システムの場合、チップとパッケージ間のTIMの熱抵抗が、パッケージ化されたモジュール全体の熱抵抗に大きな影響を与えると述べた。 特にロジックの消費電力傾向は劇的に増加しているため、当社では信頼性の高い半導体動作を保証するためにジャンクション温度を低く保つことに重点を置いています。 TIM サプライヤーは材料の熱抵抗値を提供していますが、実際には、チップからパッケージまでの熱抵抗 (ɵjc) は、チップと TIM 間の接合品質や接触面積などのアセンブリ プロセス自体の影響を受けます。 実際の熱特性を理解し、顧客検証に最適な TIM を選択するには、制御された環境で実際の組み立てツールと接合材料を使用してテストすることが重要であると彼は指摘します。

さまざまな方法で暑さに対処する

チップメーカーは、熱放散の問題を解決する方法を模索しています。 Keysight Technologies のメモリ ソリューションのプログラム マネージャ、Randy White 氏は次のように述べています。「パッケージは同じですが、チップ サイズの面積を 4 分の 1 に減らすと、速度が向上します。これにより、シグナル インテグリティに多少の違いが生じる可能性があります。ボンディング ラインが異なるため、外部パッケージの電力がチップに入る場合、配線が長ければ長いほどインダクタンスが大きくなります。そのため、十分な小さなスペースでどのようにして大量のエネルギーを消費するかが重要なパラメータとなります。勉強しました。」 これにより、ハイブリッド ボンディングに焦点を当てていると思われる最先端のボンディング研究への多額の投資が行われてきました。 しかし、ハイブリッド ボンディングのコストは高く、TSMC は現在このテクノロジーを提供している唯一の企業の 1 つであるため、依然として高性能プロセッサ タイプのアプリケーションに限定されています。 しかし、CMOSチップまたはシリコンベースの窒化ガリウム上で光子を結合する可能性は非常に有望です。

Fountyl Technologies PTE Ltdは半導体製造業界に焦点を当てており、主な製品にはピンチャック、多孔質セラミックチャック、セラミックエンドエフェクタ、セラミック角形ビーム、セラミックスピンドルが含まれます。お問い合わせと交渉を歓迎します!