칩 패키지 열 방출 문제를 해결하는 방법

고급 패키징 칩은 고성능 컴퓨팅, 인공 지능, 전력 밀도 증가 등의 요구를 충족할 수 있을 뿐만 아니라 고급 패키징의 열 방출 문제도 복잡해졌습니다. 한 칩의 핫스팟이 인접한 칩의 열 분포에 영향을 미치기 때문입니다. 칩 간의 상호 연결도 SoC보다 모듈에서 더 느립니다.

Siemens Digital Industry Software의 전자 및 반도체 산업 책임자인 John Parry는 다음과 같이 말했습니다. "세계가 멀티 코어와 같은 영역으로 이동하기 전에는 평방 센티미터당 약 150와트의 최대 전력을 가진 칩을 다루고 있었습니다. 단일 지점 열원입니다. 열을 세 방향 모두로 발산할 수 있으므로 꽤 높은 전력 밀도를 얻을 수 있습니다. 하지만 칩이 있으면 그 옆에 또 다른 칩을 놓으면 열이 발생합니다. 즉, 동일한 전력 수준을 갖는 각 칩을 견딜 수 없으므로 열 문제가 훨씬 더 어려워집니다."

이는 3D-IC 적층이 시장에서 더디게 발전하는 주된 이유 중 하나입니다. 이 개념은 전력 효율성 및 통합 관점에서 의미가 있고 3D NAND 및 HBM에서 잘 작동하지만 로직이 포함되면 이야기가 달라집니다. 로직 칩은 열을 발생시키며, 로직의 밀도가 높을수록 처리 요소의 활용도가 높아져 열도 더 커집니다. 이로 인해 논리적 스태킹이 거의 발생하지 않습니다.

올바른 패키지를 선택하세요

칩 설계자의 경우 패키징하는 방법에는 여러 가지가 있습니다. 그러나 칩 통합의 성능이 중요합니다. 실리콘, TSV 및 구리 컬럼과 같은 구성 요소는 모두 열팽창 계수(TCE)가 다르며 이는 조립 수율과 장기 신뢰성에 영향을 미칩니다.

CPU와 HBM을 갖춘 현재 인기 있는 플립 BGA 패키지의 면적은 약 2500제곱밀리미터입니다. Onto Innovation의 소프트웨어 제품 관리 책임자인 Mike McIntyre는 "큰 칩이 잠재적으로 4~5개의 작은 칩이 될 수 있는 것을 보고 있습니다. 따라서 이러한 칩이 서로 통신하려면 더 많은 I/O가 있어야 합니다. 따라서 열을 분산시킬 수 있습니다. 결국 열 방출은 시스템 수준에서만 처리할 수 있는 문제이며 일련의 절충안이 따릅니다.

실제로 일부 장치는 너무 복잡해서 특정 분야의 응용 분야에 맞게 장치를 맞춤화하기 위해 구성 요소를 쉽게 교체하기가 어렵습니다. 이것이 바로 많은 고급 패키징 제품이 서버 칩과 같이 대용량 또는 가격 탄력성이 높은 구성 요소를 위한 이유입니다.

칩 모듈 시뮬레이션 및 테스트 진행

그럼에도 불구하고 엔지니어들은 패키지 모듈이 제조되기 전에 패키지 신뢰성에 대한 열 분석을 수행할 수 있는 새로운 방법을 찾고 있습니다. 예를 들어, Siemens는 BGA 패키지의 다층 유기 기판에 팬아웃 재분배층(RDL)을 설치하는 듀얼 ASIC 기반 모듈의 예를 제공합니다. RDL 기반 WLP용 모델과 다층 유기 기판 BGA용 모델의 두 가지 모델을 사용합니다. 이러한 패키징 모델은 매개변수화되어 EDA 정보가 도입되기 전에 기판 스태킹 및 BGA를 포함하며 조기 재료 평가 및 칩 배치 선택을 가능하게 합니다. 다음으로 EDA 데이터를 가져오면 각 모델에 대해 재료 맵이 모든 레이어의 구리 분포에 대한 자세한 열 설명을 제공할 수 있습니다.

JCET의 기술 마케팅 이사인 Eric Ouyang은 JCET 및 Meta의 엔지니어들과 함께 단일 칩, 다중 칩 모듈, 2.5D 플러그 보드 및 3D 스택 칩의 열 성능을 ASIC 1개와 Sram 2개와 비교했습니다. [1] Apple 대 Apple 비교에서는 서버 환경, 진공 챔버가 있는 라디에이터 및 TIM이 변경되지 않은 상태로 유지됩니다. 열 측면에서 2.5D와 MCM은 3D 또는 단일 칩 칩보다 성능이 좋습니다.

양자화된 열저항

온도와 저항 값을 추적하기 위해 표준 온도차 및 전력 함수 방법을 사용하면서 실리콘 칩, 회로 기판, 접착제, TIM 또는 포장 캡을 통해 열이 전도되는 방식을 이해할 수 있습니다.

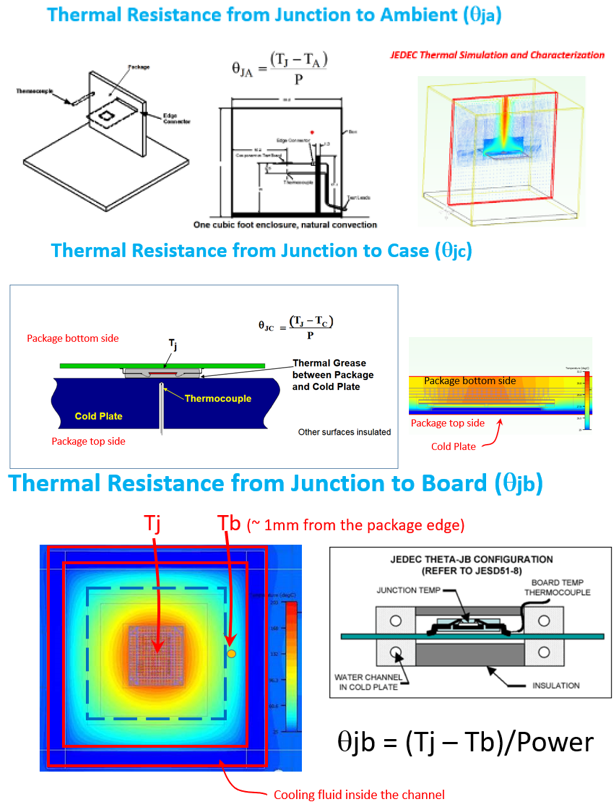

"열 경로는 장치 노드에서 환경까지의 열 저항, 노드에서 하우징(패키지 상단)까지의 열 저항, 노드에서 보드까지의 열 저항이라는 세 가지 주요 값으로 정량화됩니다. "라고 JCET의 Ouyang은 말합니다. 그는 최소한 JCET의 고객에게는 ɵja, ɵjc 및 ɵjb가 필요하며 이를 시스템 설계에 사용한다고 지적합니다. 주어진 열 저항이 특정 값을 초과하지 않아야 하며 패키지 설계가 해당 성능을 제공해야 할 수도 있습니다.

열 시뮬레이션은 재료의 선택과 배치를 탐색하는 가장 경제적인 방법입니다. 작동 상태의 칩 시뮬레이션을 통해 우리는 일반적으로 하나 이상의 핫스팟을 발견하므로 열 방출을 촉진하기 위해 핫스팟 아래의 기판에 구리를 추가할 수 있습니다. 또는 포장재를 변경하고 라디에이터를 늘리십시오. 시스템 통합자는 열 저항 ɵja, ɵjc 및 ɵjb가 특정 값을 초과하지 않도록 지정할 수 있습니다. 일반적인 상황에서 실리콘 접합 온도는 125°C 미만으로 유지되어야 합니다. 시뮬레이션이 완료된 후 패키징 공장에서는 DOE(실험 설계)를 수행하여 최종 패키지 계획에 도달합니다.

TIM 선택

패키지에서는 90% 이상의 열이 패키지를 통해 칩 상단부터 일반적으로 양극 산화 처리된 알루미늄을 기반으로 하는 수직 핀인 라디에이터까지 방출됩니다. 열전도율이 높은 TIM(Thermal Interface Material)을 칩과 패키지 사이에 배치해 열 전달을 돕습니다. CPU용 차세대 TIM에는 인듐, 주석 등의 판금 합금과 전도성이 각각 60W/mK, 50W/mK인 은소결 주석이 포함됩니다. 공급업체가 SoC를 칩렛 프로세스로 전환함에 따라 다양한 특성과 두께를 가진 더 많은 TIM이 필요합니다.

앰코의 권영도 연구개발 수석 이사는 고밀도 시스템의 경우 칩과 패키지 사이의 TIM의 열 저항이 패키지 모듈의 전체 열 저항에 더 큰 영향을 미친다고 말했습니다. 특히 로직의 경우 전력 추세가 급격히 증가하고 있으므로 안정적인 반도체 작동을 보장하기 위해 접합 온도를 낮게 유지하는 데 중점을 두고 있습니다. TIM 공급업체는 재료에 대한 열 저항 값을 제공하지만 실제로 칩에서 패키지까지의 열 저항(ɵjc)은 칩과 TIM 사이의 접합 품질 및 접촉 면적을 포함하여 조립 공정 자체의 영향을 받습니다. 그는 통제된 환경에서 실제 조립 도구와 접합 재료를 사용한 테스트가 실제 열 특성을 이해하고 고객 검증을 위한 최고의 TIM을 선택하는 데 중요하다고 지적합니다.

다양한 방법으로 더위를 다루려면

칩 제조사들은 열 방출 문제를 해결할 수 있는 방법을 찾고 있습니다. 키사이트테크놀로지스의 메모리 솔루션 프로그램 관리자인 Randy White는 "패키지는 동일합니다. 칩 크기 영역을 1/4로 줄이면 속도가 빨라질 것입니다. 이로 인해 신호 무결성에 약간의 차이가 발생할 수 있습니다. 본딩 라인이 외부 패키지가 칩에 들어가게 되는데, 라인이 길어질수록 인덕턴스가 커지므로 전기적 성능 부분이 생깁니다. 그렇다면 충분히 작은 공간에서 그 많은 에너지를 어떻게 소비해야 할까요? 공부했어요." 이로 인해 하이브리드 본딩에 초점을 맞춘 것으로 보이는 최첨단 본딩 연구에 상당한 투자가 이루어졌습니다. 그러나 하이브리드 본딩 비용은 높으며 여전히 고성능 프로세서 유형 애플리케이션으로 제한되어 있으며, TSMC는 현재 이 기술을 제공하는 유일한 회사 중 하나입니다. 그러나 CMOS 칩이나 실리콘 기반 질화갈륨에서 광자를 결합할 가능성은 매우 유망합니다.

Fountyl Technologies PTE Ltd는 반도체 제조 산업에 주력하고 있으며 주요 제품은 다음과 같습니다: 핀 척, 다공성 세라믹 척, 세라믹 엔드 이펙터, 세라믹 사각 빔, 세라믹 스핀들, 연락 및 협상 환영!