industri kerepek. Istilah teknikal dan singkatan. Analisis grafik kata nama

Pembuatan

TAPEOUT(TO): Ini bermaksud menyerahkan fail GDSII terakhir kepada Foundry untuk diproses.

TOPENG PENUH: Iaitu, semua topeng dalam proses pembuatan berfungsi dengan reka bentuk tertentu.

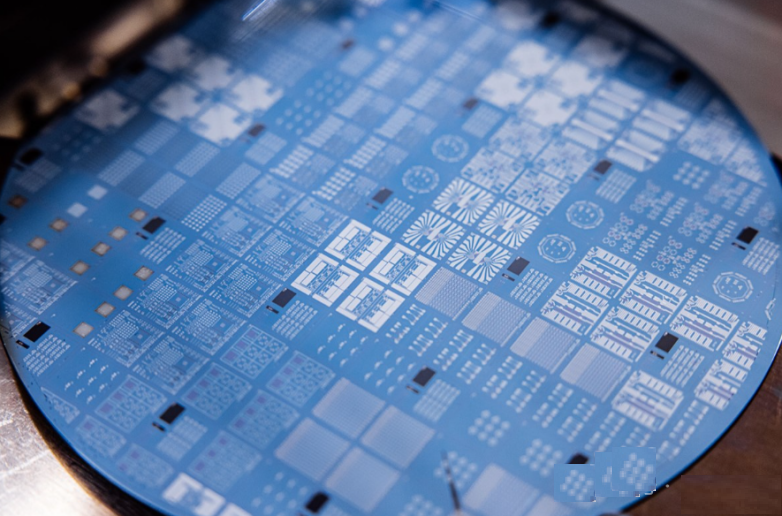

MPW (Wafer Berbilang Projek):Iaitu, berbilang projek berkongsi wafer, iaitu, proses pembuatan yang sama boleh melaksanakan tugas pembuatan berbilang reka bentuk IC.

MPW akan berkongsi plat MASK dengan pengeluar lain, dan FULL MASK adalah untuk menikmati sendiri plat mask. Jika risiko cip agak tinggi, anda boleh melakukan MPW terlebih dahulu, jika ujian tiada masalah, dan kemudian lakukan FULL MASK.

Faundri:Specializ ed dalam pengeluar pembuatan cip, seperti Taiwan Semiconductor Manufacturing (TSMC), Semiconductor Manufacturing International (SMIC), United Electric (UMC). Yang sepadan adalah fabless, adalah pengeluar reka bentuk, cuma tiada fab.

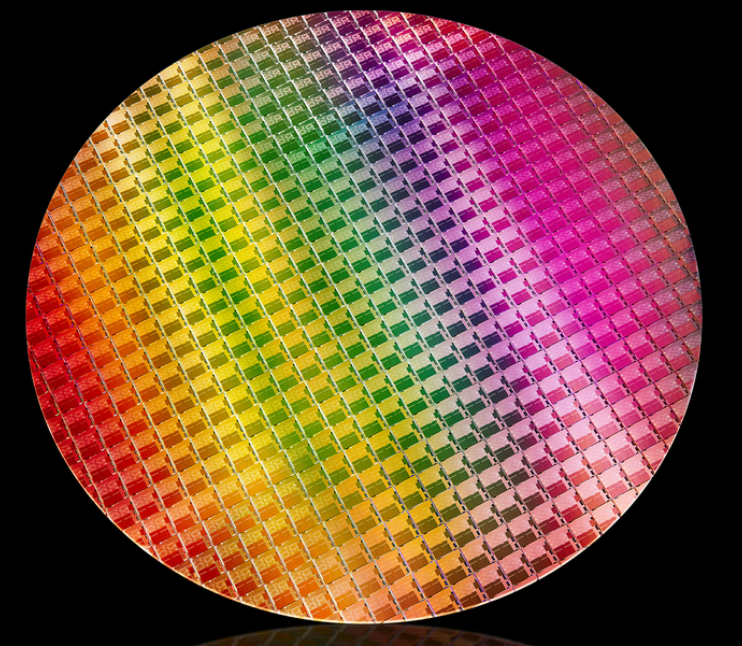

wafer

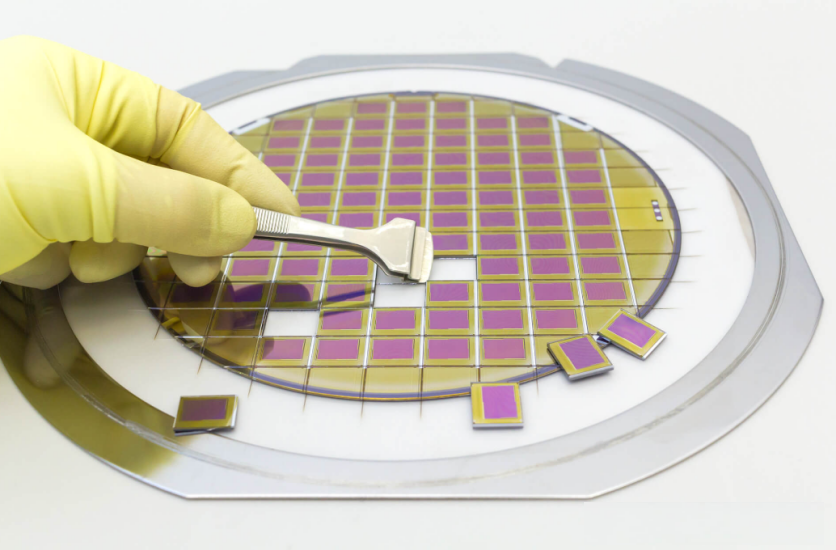

yang:Selepas wafer dipotong, wafer daripada cip tunggal, yang perlu menambah cangkerang tertutup untuk menjadi cip.

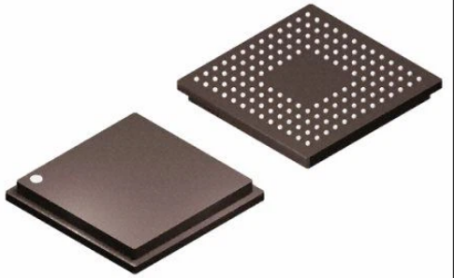

Cip:Pakej akhir cip

Benjolan: bumping merujuk kepada bumping point. Selepas titik cembung (emas, plumbum timah, bebas plumbum...dll) ditanam pada permukaan wafer, (kebanyakannya digunakan pada pakej proses flip, iaitu flipchip).

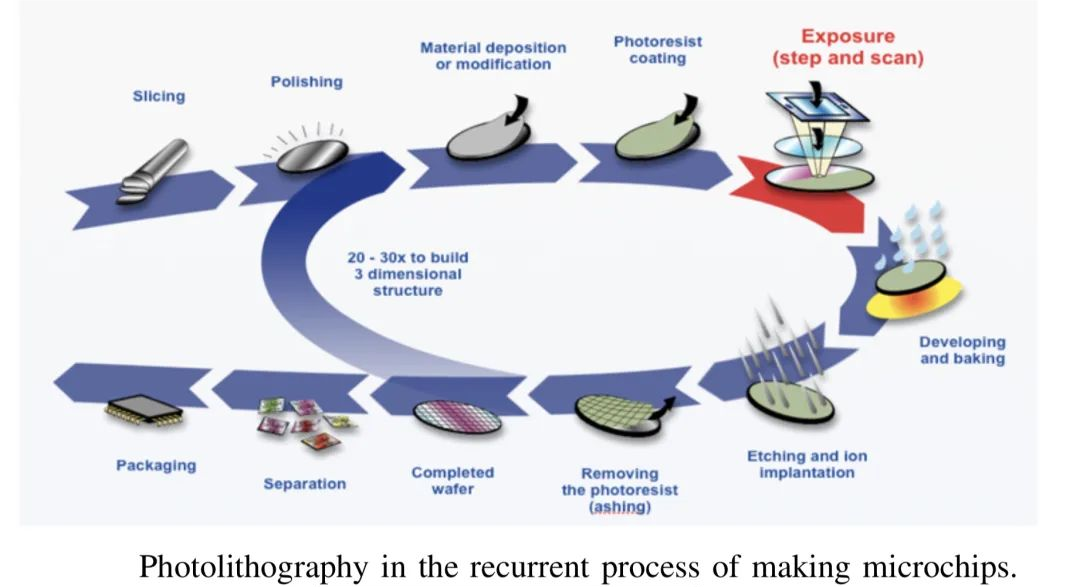

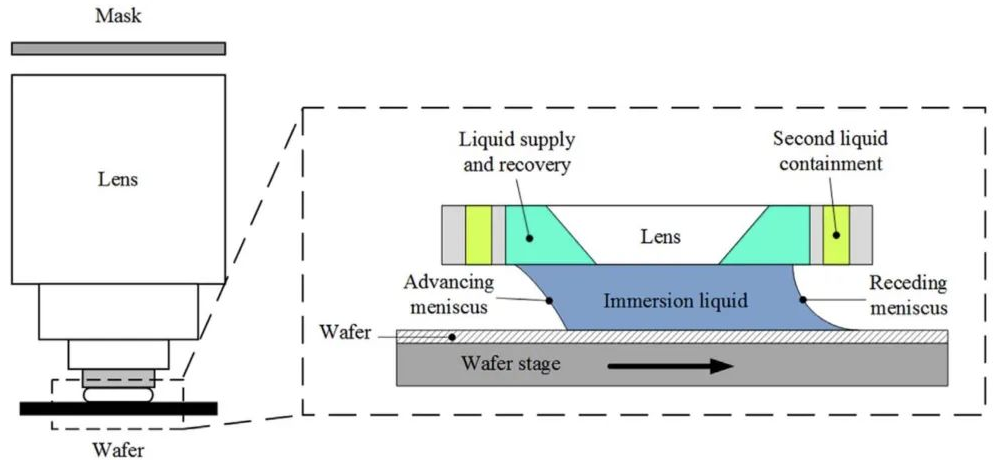

Topeng :Topeng templat grafik legap di kawasan yang dipilih pada wafer, dan kakisan atau resapan berikutnya hanya akan menjejaskan kawasan di luar kawasan yang dipilih

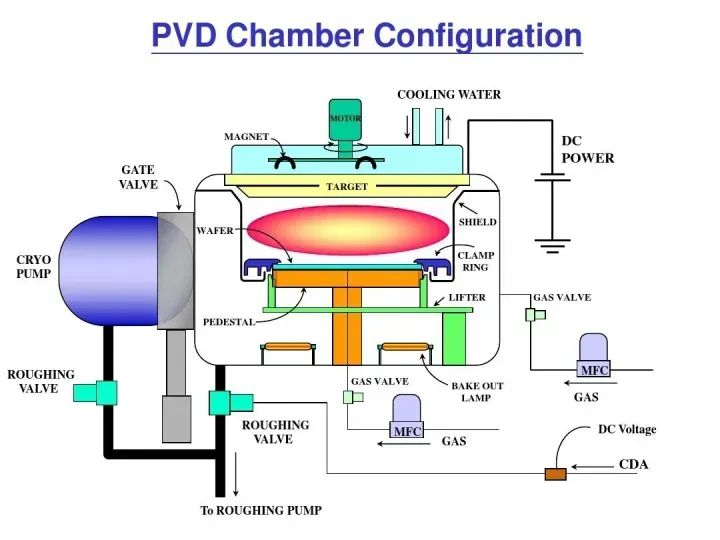

Chamber:Merujuk kepada ruang terkurung dan mempunyai tujuan khas, seperti penyedutan, tindak balas gas atau percikan logam.

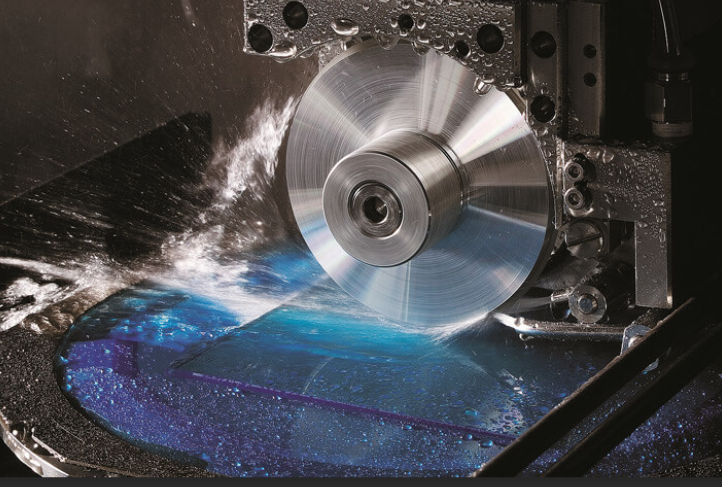

Wafer Dicing: Wafermemotong dadu, memotong wafer

CVD (Pemendapan Wap Kimia): Ia adalah teknologi canggih yang digunakan secara meluas dalam bidang penyediaan bahan, menggunakan persekitaran suhu tinggi dan tekanan rendah untuk menukar bahan kimia dalam gas atau campuran gas kepada bahan pepejal.

PVD (Pemendapan Wap Fizikal): Kaedah melekatkan bahan lain pada permukaan substrat dengan teknologi plasma ion. Adakah nama am semburan, penyejatan...dll.

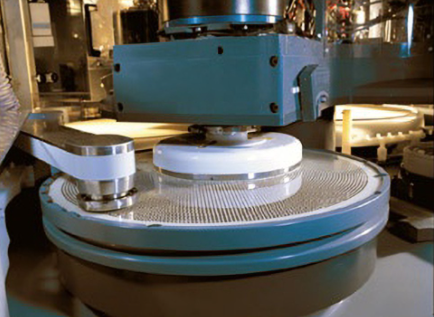

CMP (Chemical-Mechincal Polish): Tdia menggunakan pad pengisaran (polishingpad) yang ditutup dengan zarah pengisaran pada permukaan, , dengan bantuan bahan tambahan kimia (reagen), dengan tindak balas kimia dan pengisaran mekanikal tindakan pemprosesan berganda, untuk menjalankan rawatan kerataan permukaan pada permukaan kristal yang tidak rata .

CDA (Udara Kering Bersih): Biasanya merujuk kepada udara dengan tekanan antara 60 dan 110psi, yang telah ditulenkan dan dikeringkan. Sebagai sumber gas untuk komponen pneumatik.

Penyebaran: Dalam industri semikonduktor, ia sering digunakan sebagai sumber resapan pada cip silikon yang sangat tulen dengan pratetap atau implantasi ion, dan resapan selesai dalam beberapa jam dengan menambahkan suhu tinggi ke tiub relau.

Air DI: Air paip atau air bawah tanah, yang mengandungi sejumlah besar bakteria, ion logam dan zarah, mesti disterilkan dan disucikan oleh peralatan, dan kemudian kekotoran ion logam dikeluarkan, air Terhasil dipanggil "air ternyahion". Direka untuk pembuatan IC.

Dopan: Dalam bahan semikonduktor asal, implantasi aktif atau penggabungan atom atau ion lain melalui resapan untuk mengubah sifat elektriknya.

Dummy Wafer : Wafer silikon yang memainkan peranan tambahan tertentu dalam proses, membezakan daripada produk. Secara amnya, keperluan kualiti tidak begitu tinggi.

Reka bentuk

Fabless: ialah gabungan fabrikasi dan kurang, yang merujuk kepada mod operasi reka bentuk litar bersepadu dengan "tiada perniagaan pembuatan dan hanya fokus pada reka bentuk". Ia juga digunakan untuk merujuk kepada syarikat reka bentuk IC yang tidak memiliki kilang pembuatan cip.

RTL (Tahap Daftar-Pemindahan): Ia adalah bahasa penerangan perkakasan yang digunakan untuk menerangkan litar digital segerak.

SDC(Synopsys Design Chip) :Reka bentuk menyediakan fail kekangan yang diperlukan oleh alat sintesis untuk menukar RTL kepada netlist. Penerangan utama SDC termasuk: kekerapan operasi cip, pemasaan IO cip, peraturan reka bentuk, laluan khas, laluan tanpa semakan, dan sebagainya.

Pengesahan fungsi cip: Ia terutamanya merujuk kepada metodologi pengesahan cip, mengesahkan sama ada RTL dan model rujukan adalah konsisten.

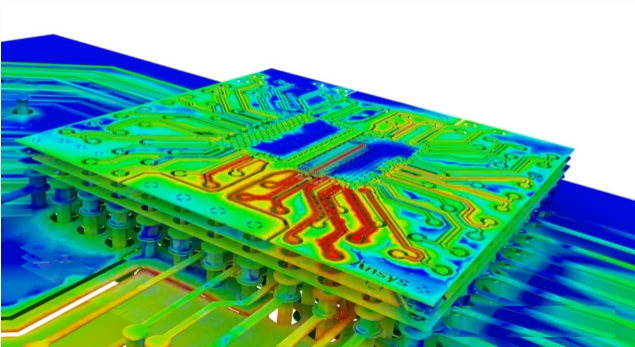

Simulasi: simulasi biasanya dijana bentuk gelombang, secara amnya, fungsi cip, pengesahan, penggunaan kuasa cip, boleh disimulasikan, refleksi yang lebih intuitif adegan sebenar.

IP (Harta Intelek):aset reka bentuk, modul litar berfungsi (teras, unit) yang telah direka bentuk

DesignRule:Oleh kerana teknologi proses semikonduktor adalah teknologi profesional, halus dan kompleks, terdedah kepada pengaruh kaedah proses peralatan pembuatan yang berbeza (RESEPI), adalah perlu untuk mempunyai satu set spesifikasi untuk melakukan peruntukan teknikal apabila mempertimbangkan cara melibatkan diri dalam teknologi pembuatan kesempurnaan dan kejayaan pembuatan pelbagai produk, iaitu "DesignRule". Ia dirumus mengikut keperluan, spesifikasi, peralatan pembuatan dan kaedah proses, keupayaan proses, dan parameter elektrik berkaitan pelbagai produk.

UJIAN

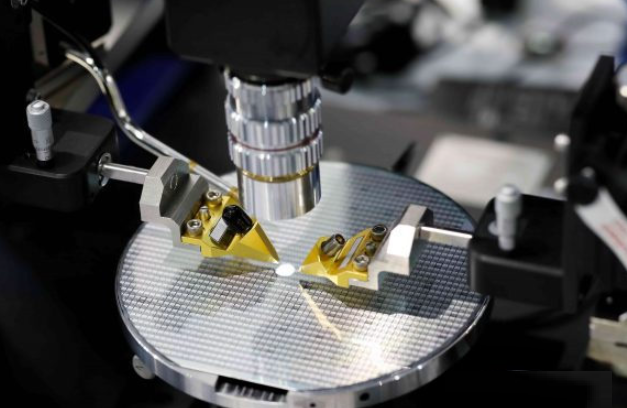

CP(Chip Probing):Uji wafer secara terus, dan objek ujian adalah untuk setiap Die dalam keseluruhan wafer, tujuannya adalah untuk memastikan setiap Die dalam keseluruhan wafer pada asasnya boleh memenuhi ciri peranti atau spesifikasi reka bentuk, biasanya termasuk pengesahan untuk voltan, arus, masa dan fungsi, Ia boleh digunakan untuk menguji tahap proses pembuatan di kilang fab.

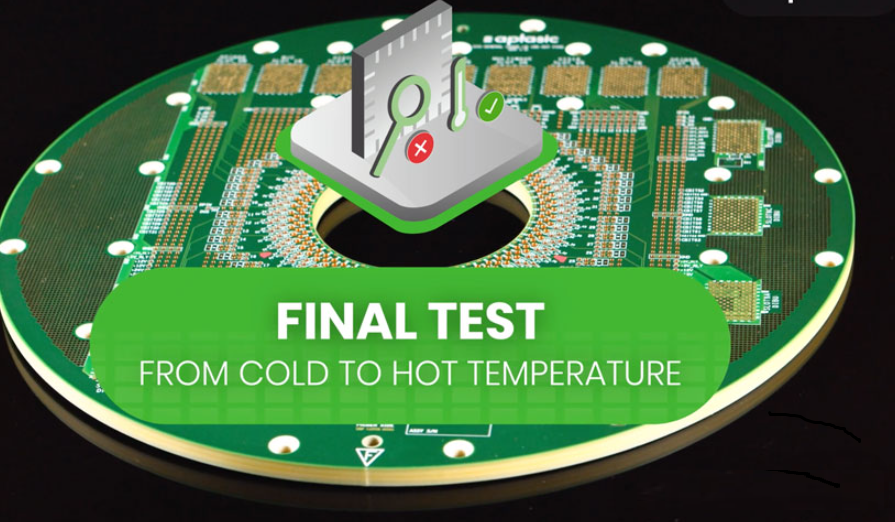

FT(Ujian Akhir): Ini adalah pintasan terakhir sebelum cip meninggalkan kilang. Objek ujian adalah untuk cip terkapsul, yang akan dikapsulkan selepas ujian CP dan kemudian ujian FT selepas enkapsulasi. Ia boleh digunakan untuk menguji tahap teknikal kilang pembungkusan.

CP untuk wafer, jika Die buruk tidak perlu melakukan pembungkusan, menjimatkan kos pembungkusan dan kos substrat.

Selepas ujian CP selesai, kegagalan cip akan diperkenalkan dalam proses pembungkusan, jadi FT juga diperlukan untuk mengeluarkan cip yang gagal.

Hasil: Hasil cip adalah berkaitan dengan proses, cip mempunyai kebarangkalian kegagalan tertentu, dan semakin besar cip, semakin besar kebarangkalian kegagalan.

IP(Harta Intelek):Dalam reka bentuk litar bersepadu, modul berfungsi lengkap bagi litar bersepadu Terbukti dan boleh diguna semula dengan fungsi tertentu.

Pelbagai IP boleh dibahagikan kepada Lesen, Kesetiaan setiap cara kutipan tol

lesen Kebenaran Lesen: kebenaran untuk menggunakan IP ini, kebenaran IP.

Royalti kesetiaan: Selepas pengguna menggunakan IP, mereka dicaj setiap cip.

IP adalah komponen teras cip, seperti USB, PCIE, CPU adalah IP, keseluruhan cip adalah IP bersepadu, cip boleh melakukan lebih kompleks, teras adalah penggunaan semula IP. Sebagai contoh, mereka yang membuat berpuluh-puluh juta pintu, ratusan juta pintu, adalah penggunaan semula IP boleh dilakukan.

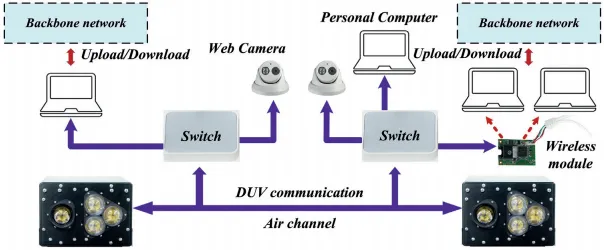

DUV (Sinar Ultraviolet Dalam) EUV (Sinar Ultraviolet Melampau )

Pembungkusan

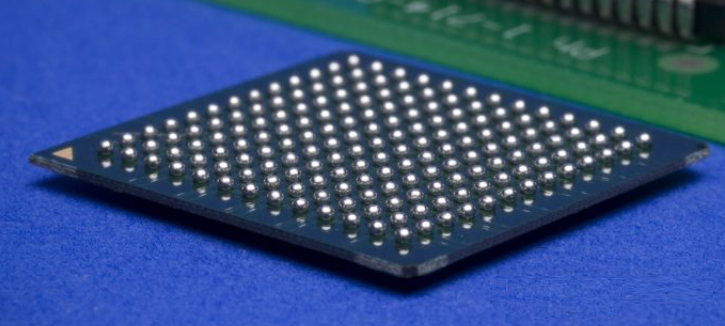

BGA (Ball Grid Array): Sejenis pakej yang dipasang di permukaan di mana beberapa bola pateri yang disambungkan disusun pada substrat yang dipasang cip (susun grid bola).

ASIC(Litar Bersepadu Khusus Aplikasi): ASIC ialah cip khas, yang merupakan istilah umum untuk cip yang disesuaikan khas untuk keperluan tertentu. Contohnya, pemproses audio dan video yang berdedikasi, dan pada masa ini, banyak industri cip AI yang berdedikasi boleh dianggap sebagai sejenis ASIC.

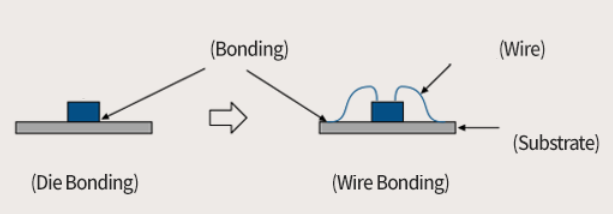

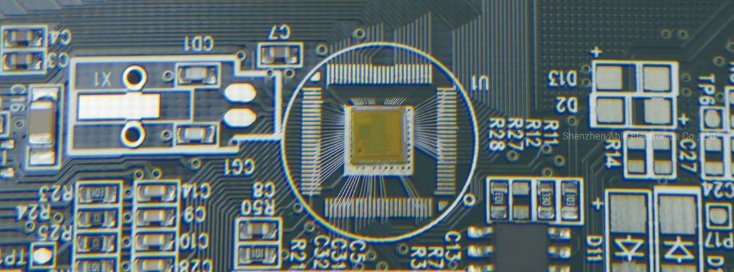

Wirebonding: Wire Bonding (press welding, also known as binding, bonding, wire welding) merujuk kepada penggunaan dawai logam (dawai emas, dawai aluminium...dll.), penggunaan tekanan panas atau tenaga ultrasonik untuk melengkapkan sambungan pendawaian dalaman litar keadaan pepejal, iaitu sambungan antara cip dan litar atau bingkai plumbum.

Die terikat:

Flipchip: Bola plumbum timah didepositkan pada I/Opad, dan kemudian cip dibalikkan dan dipanaskan menggunakan bola plumbum timah cair yang digabungkan dengan substrat seramik.

COB (chip-on-board):Pembungkusan cip atas papan adalah untuk memasang cip kosong pada PCB dengan pelekat konduktif atau bukan konduktif, dan kemudian melakukan ikatan plumbum untuk mencapai sambungan elektriknya, dan membungkus cip dan ikatan plumbum dengan pelekat.

SOC(System On Chip): Adalah untuk meletakkan CPU, bas, peranti...dll., ke dalam pelaksanaan dalaman cip. Sebagai contoh, pemproses telefon mudah alih ialah cip SOC yang kompleks.

SIP (System In Package): Pakej SiP ialah cip mentah dengan fungsi yang berbeza, termasuk CPU, GPU, memori...dsb. disepadukan dalam badan pakej, untuk mencapai keseluruhan sistem cip.

SOP(Pakej Rangka Kecil):Pakej luaran kecil pakej IC di mana petunjuk ditarik ke kedua-dua arah

DAF (Die Attach Film): Teknologi ikatan filem pengikatan wafer

CMOS (Separuh Pengalir Oksida Logam Pelengkap): Semikonduktor oksida logam pelengkap. Ia merujuk kepada teknologi yang digunakan untuk membuat cip litar bersepadu berskala besar, atau cip yang dibuat menggunakan teknologi ini, iaitu sekeping cip RAM yang boleh dibaca dan ditulis pada papan induk komputer. Kerana ciri baca-tulis, ia digunakan untuk menyimpan data BIOS selepas parameter perkakasan komputer ditetapkan pada papan induk komputer, dan cip ini hanya digunakan untuk menyimpan data.

JEDEC (Piawaian Majlis Kejuruteraan Peranti Elektron Bersama): Spesifikasi standard AS untuk dimensi pakej.

Fountyl Technologies PTE Ltd, memberi tumpuan kepada industri pembuatan semikonduktor, produk utama termasuk: Pin chuck, poros ceramic chuck, seramik end effector, seramik square rasuk, seramik spindle, dialu-alukan untuk menghubungi dan rundingan!