Bagaimana untuk menyelesaikan masalah pelesapan haba pakej cip

Cip pembungkusan lanjutan bukan sahaja dapat memenuhi keperluan pengkomputeran berprestasi tinggi, kecerdasan buatan, pertumbuhan ketumpatan kuasa, dan lain-lain, tetapi juga masalah pelesapan haba pembungkusan lanjutan telah menjadi rumit. Kerana titik panas pada satu cip menjejaskan taburan haba cip jiran. Sambungan antara cip juga lebih perlahan dalam modul berbanding dalam SoC.

John Parry, ketua industri elektronik dan semikonduktor di Perisian Industri Digital Siemens, berkata: "Sebelum dunia bergerak ke kawasan seperti berbilang teras, anda berurusan dengan cip yang mempunyai kuasa maksimum kira-kira 150 watt setiap sentimeter persegi, yang sumber haba satu titik Anda boleh menghilangkan haba dalam ketiga-tiga arah, supaya anda boleh mencapai beberapa ketumpatan kuasa yang cukup tinggi, tetapi apabila anda mempunyai cip, letakkan cip lain di sebelahnya, dan kemudian letakkan cip lain di sebelahnya, ia panas satu sama lain. Ini bermakna anda tidak boleh bertolak ansur dengan setiap cip yang mempunyai tahap kuasa yang sama, yang menjadikan cabaran terma lebih sukar."

Ini adalah salah satu sebab utama mengapa tindanan 3D-IC membuat kemajuan yang perlahan dalam pasaran. Walaupun konsep itu masuk akal dari sudut kecekapan kuasa dan penyepaduan - dan berfungsi dengan baik dalam 3D NAND dan HBM - ia adalah cerita yang berbeza apabila logik disertakan. Cip logik menghasilkan haba, dan lebih padat logik, lebih tinggi penggunaan elemen pemprosesan, lebih besar haba. Ini menjadikan susunan logik jarang berlaku.

Pilih pakej yang betul

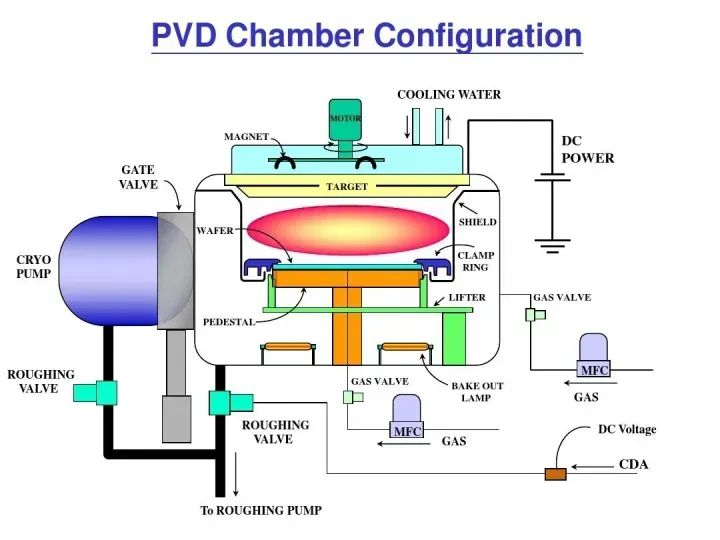

Bagi pereka cip, terdapat banyak cara untuk membungkus. Tetapi prestasi penyepaduan cip adalah penting. Komponen seperti silikon, TSV dan lajur tembaga semuanya mempunyai pekali pengembangan terma (TCE) yang berbeza, yang menjejaskan hasil pemasangan dan kebolehpercayaan jangka panjang.

Pakej flip BGA semasa yang popular dengan cpu dan HBM mempunyai keluasan kira-kira 2500 milimeter persegi. Mike McIntyre, ketua pengurusan produk perisian di Onto Innovation, berkata: "Kami melihat cip besar berpotensi menjadi empat atau lima cip kecil. Jadi anda perlu mempunyai lebih banyak I/O agar cip ini bercakap antara satu sama lain. Jadi anda boleh mengedarkan haba Akhirnya, pelesapan haba adalah masalah yang hanya boleh ditangani di peringkat sistem, dan ia datang dengan satu siri pertukaran.

Malah, sesetengah peranti adalah sangat kompleks sehingga sukar untuk menggantikan komponen dengan mudah untuk menyesuaikan peranti ini untuk aplikasi dalam bidang tertentu. Inilah sebabnya mengapa banyak produk pembungkusan termaju adalah untuk komponen volum yang sangat tinggi atau harga-anjal, seperti cip pelayan.

Kemajuan dalam simulasi dan ujian modul cip

Namun begitu, jurutera sedang mencari cara baharu untuk melaksanakan analisis terma kebolehpercayaan pakej sebelum modul yang dibungkus dihasilkan. Sebagai contoh, Siemens menyediakan contoh modul berasaskan ASIC dwi yang memasang lapisan pengagihan semula kipas (RDL) pada substrat organik berbilang lapisan dalam pakej BGA. Ia menggunakan dua model, satu untuk WLP berasaskan RDL dan satu lagi untuk substrat organik berbilang lapisan BGA. Model pembungkusan ini diparameterkan, termasuk susunan substrat dan BGA sebelum maklumat EDA diperkenalkan, dan membolehkan penilaian bahan awal dan pemilihan peletakan cip. Seterusnya, data EDA diimport, dan bagi setiap model, peta bahan dapat memberikan penerangan terperinci tentang pengedaran kuprum dalam semua lapisan.

Eric Ouyang, Pengarah Pemasaran Teknikal di JCET, bersama-sama dengan jurutera dari JCET dan Meta, membandingkan prestasi terma bagi modul cip tunggal, berbilang cip, papan pemalam 2.5D dan cip bertindan 3D dengan satu ASIC dan dua Sram. [1] Perbandingan Apple-to-Apple meninggalkan persekitaran pelayan, radiator dengan ruang vakum dan TIM tidak berubah. Dari segi haba, 2.5D dan MCM berprestasi lebih baik daripada cip 3D atau cip tunggal.

Rintangan haba terkuantiti

Kita boleh memahami bagaimana haba dijalankan melalui cip silikon, papan litar, gam, TIM atau penutup pembungkusan, sambil menggunakan kaedah standard perbezaan suhu dan fungsi kuasa untuk mengesan suhu dan nilai rintangan.

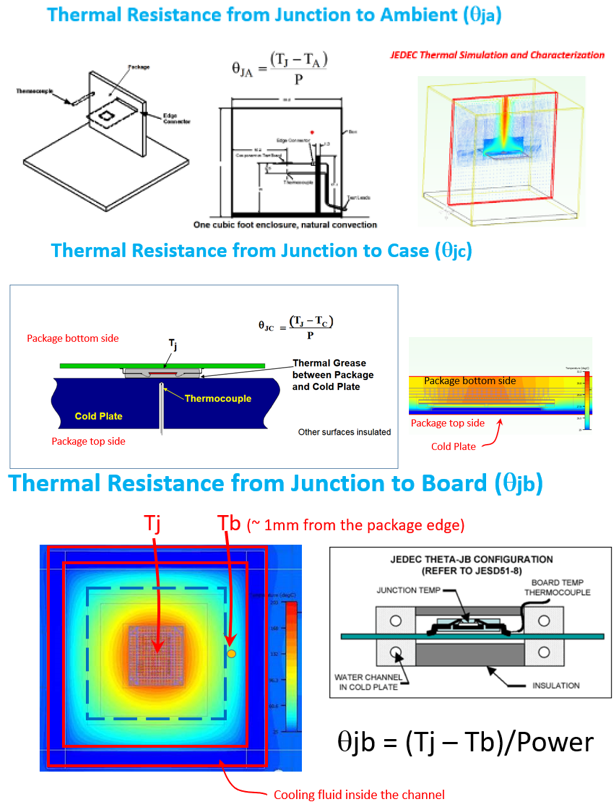

"Laluan terma dikira dengan tiga nilai utama - rintangan haba dari nod peranti ke persekitaran, rintangan haba dari nod ke perumah [di bahagian atas pakej], dan rintangan haba dari nod ke papan ," kata Ouyang JCET. Sekurang-kurangnya, beliau menegaskan, pelanggan JCET memerlukan ɵja, ɵjc dan ɵjb, yang kemudiannya mereka gunakan dalam reka bentuk sistem. Mereka mungkin memerlukan rintangan haba yang diberikan tidak melebihi nilai tertentu dan reka bentuk pakej memberikan prestasi tersebut.

Simulasi terma ialah cara paling menjimatkan untuk meneroka pemilihan dan kolokasi bahan. Melalui simulasi cip dalam keadaan kerja, kami biasanya mencari satu atau lebih titik panas, jadi kami boleh menambah tembaga ke substrat di bawah titik panas untuk memudahkan pelesapan haba; Atau tukar bahan pembungkusan, tambah radiator. Penyepadu sistem boleh menentukan bahawa rintangan haba ɵja, ɵjc, dan ɵjb tidak boleh melebihi nilai tertentu. Dalam keadaan biasa, suhu simpang silikon hendaklah dikekalkan di bawah 125 ° C. Selepas simulasi selesai, kilang pembungkusan menjalankan reka bentuk eksperimen (JAS) untuk tiba di pelan pakej akhir.

Pilih TIM

Dalam bungkusan, lebih daripada 90% haba dilesapkan melalui bungkusan dari bahagian atas cip ke radiator, yang biasanya sirip menegak berdasarkan aluminium anodized. Bahan antara muka terma (TIM) dengan kekonduksian terma yang tinggi diletakkan di antara cip dan bungkusan untuk membantu memindahkan haba. TIM generasi seterusnya untuk cpus termasuk aloi logam lembaran seperti indium dan timah, serta timah tersinter perak dengan kekonduksian masing-masing 60W/mK dan 50W/mK. Apabila vendor mengalihkan SoC kepada proses ciplet, lebih banyak TIM dengan sifat dan ketebalan yang berbeza diperlukan.

YoungDo Kweon, pengarah kanan penyelidikan dan pembangunan di Amkor, berkata bahawa untuk sistem berketumpatan tinggi, rintangan haba TIM antara cip dan pakej mempunyai kesan yang lebih besar terhadap rintangan haba keseluruhan modul yang dibungkus. Aliran kuasa meningkat secara mendadak, terutamanya untuk logik, jadi kami menumpukan pada mengekalkan suhu simpang rendah untuk memastikan operasi semikonduktor yang boleh dipercayai. Walaupun pembekal TIM memberikan nilai rintangan haba untuk bahan mereka, sebenarnya, rintangan haba dari cip ke pakej (ɵjc) dipengaruhi oleh proses pemasangan itu sendiri, termasuk kualiti ikatan dan kawasan sentuhan antara cip dan TIM. Beliau menyatakan bahawa ujian dengan alat pemasangan sebenar dan bahan ikatan dalam persekitaran terkawal adalah penting untuk memahami sifat terma sebenar dan memilih TIM terbaik untuk pengesahan pelanggan.

Untuk menangani haba dengan cara yang berbeza

Pembuat cip sedang mencari cara untuk menyelesaikan masalah pelesapan haba. Randy White, pengurus program untuk penyelesaian memori di Keysight Technologies, berkata: "Pakej adalah sama, jika anda mengurangkan kawasan saiz cip sebanyak satu perempat, ia akan mempercepatkan. Ini mungkin menyebabkan beberapa perbezaan integriti isyarat. Kerana garis ikatan daripada pakej luaran akan memasuki cip, semakin panjang garisan, semakin besar kearuhan, jadi terdapat bahagian prestasi elektrik Jadi bagaimana anda menggunakan tenaga sebanyak itu dalam ruang yang cukup kecil. Ini adalah satu lagi parameter utama yang perlu belajar." Ini telah membawa kepada pelaburan yang besar dalam penyelidikan ikatan canggih yang nampaknya memberi tumpuan kepada ikatan hibrid. Tetapi kos ikatan hibrid adalah tinggi, dan ia masih terhad kepada aplikasi jenis pemproses berprestasi tinggi, dengan TSMC menjadi satu-satunya syarikat yang menawarkan teknologi ini pada masa ini. Walau bagaimanapun, prospek untuk menggabungkan foton pada cip CMOS atau galium nitrida berasaskan silikon adalah sangat menjanjikan.

Fountyl Technologies PTE Ltd, memberi tumpuan kepada industri pembuatan semikonduktor, produk utama termasuk: Pin chuck, poros ceramic chuck, seramik end effector, seramik square rasuk, seramik spindle, dialu-alukan untuk menghubungi dan rundingan!