Teknologi dan peralatan semikonduktor: ujian cip dan peralatan

Pengujian adalah cara penting untuk memastikan fungsi dan hasil. Ujian cip boleh dibahagikan kepada dua bahagian utama. CP(cip probering) dan FT(ujian akhir). Sesetengah cip juga melakukan SLT (ujian tahap sistem). Terdapat juga keperluan khusus untuk cip yang memerlukan beberapa ujian kebolehpercayaan.

ujian CP

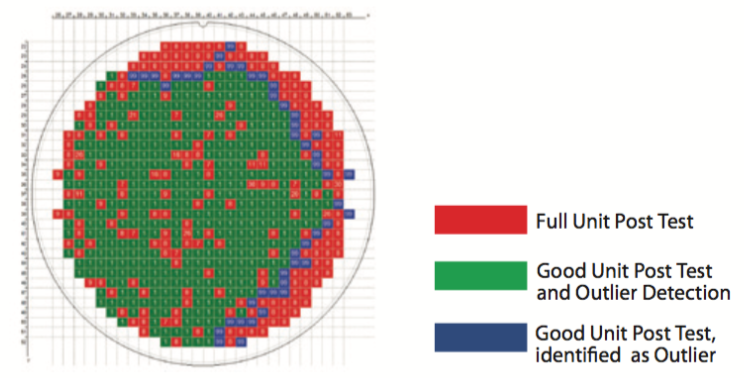

Ujian CP (Chip Probing) juga dipanggil ujian wafer, iaitu menguji wafer sebelum cip tidak dibungkus, supaya cip yang bermasalah dapat dikeluarkan sebelum pembungkusan, menjimatkan kos pembungkusan dan FT. Ujian CP terletak di antara fabrikasi wafer dan pembungkusan sepanjang proses membuat cip. Selepas Wafer dibuat, beribu-ribu dadu telanjang (cip tidak dibungkus) sentiasa diisi dengan keseluruhan Wafer. Oleh kerana cip belum dihiris, pin cip semuanya terdedah, dan pin yang sangat kecil ini perlu disambungkan kepada Penguji melalui Prober yang lebih nipis.

Ujian CP terutamanya mengukur aspek berikut:

1.SCAN: untuk menyemak sama ada fungsi logik cip adalah betul atau tidak.

2. Boundary SCAN: untuk memeriksa sama ada fungsi pin cip betul atau tidak.

3. Memori: Cip sering disepadukan dengan pelbagai jenis memori (seperti ROM/RAM/Flash). Untuk menguji memori baca dan tulis serta fungsi penyimpanan, logik BIST (Built-In SelfTest) biasanya ditambah terlebih dahulu semasa reka bentuk untuk ujian kendiri memori. Cip memasuki pelbagai fungsi BIST melalui konfigurasi pin khas, dan modul BIST memberi maklum balas keputusan ujian kepada Penguji selepas selesai ujian kendiri.

4. Ujian DC/AC: Ujian DC termasuk ujian Terbuka/Pendek untuk PIN Isyarat cip, ujian PowerShort untuk PIN kuasa dan ujian untuk melihat sama ada parameter arus dan voltan DC cip memenuhi spesifikasi reka bentuk atau tidak.

5. Ujian RF: Untuk cip komunikasi tanpa wayar, fungsi dan prestasi RF adalah penting. Ujian RF dilakukan dalam CP untuk memeriksa sama ada fungsi logik modul RF adalah betul. Ujian prestasi selanjutnya juga dilakukan pada RF di FT.

6. Ujian Fungsi Lain: ia digunakan untuk menguji sama ada fungsi dan prestasi penting lain cip memenuhi spesifikasi reka bentuk atau tidak.

7. Lebih dekat wafer dengan tepi, lebih besar peluang dadu (cek kecil, iaitu cip yang tidak dibungkus) menjadi salah.

FT(ujian akhir)

FT(ujian akhir) ialah ujian akhir, yang dijalankan selepas cip dibungkus. Ujian FT ialah ujian tahap cip yang mewujudkan sambungan elektrik antara peranti ujian automatik (ATE) dan cip yang dibungkus melalui Papan Muatan dan Soket ujian. Tujuan ujian FT adalah untuk memilih produk yang memenuhi spesifikasi reka bentuk untuk dijual kepada pelanggan.

Projek ujian FT juga ditentukan mengikut fungsi dan ciri cip. Item ujian FT biasa ialah:

1, Ujian terbuka/pendek: untuk memeriksa sama ada terdapat litar terbuka atau pintas dalam pin cip.

2, ujian DC: untuk memeriksa parameter arus dan voltan DC peranti.

3. Ujian Eflash: untuk menyemak fungsi dan prestasi denyar terbenam, termasuk pelbagai parameter membaca dan menulis, tindakan, penggunaan kuasa dan kelajuan.

4, Ujian fungsi: untuk menguji fungsi logik cip.

5, ujian AC: untuk mengesahkan spesifikasi AC, termasuk kualiti isyarat keluaran AC dan parameter sebenar isyarat.

6, Ujian RF: Ini adalah untuk cip dengan modul RF, terutamanya untuk mengesahkan fungsi dan parameter prestasi modul RF.

7. Ujian DFT: Reka Bentuk untuk Ujian, terutamanya termasuk reka bentuk imbasan dan ujian kendiri bahagian dalaman, iaitu BIST (Bina Dalam Ujian Sendiri).

SLT

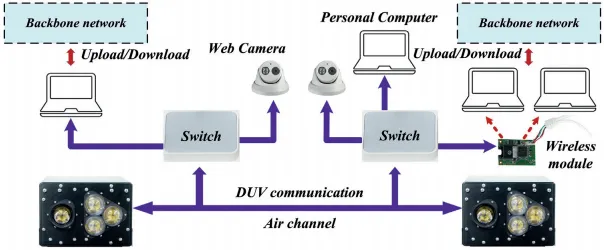

SLT ialah singkatan Ujian Tahap Sistem. SLT digunakan apabila kadar liputan ujian lain tidak dapat dipenuhi. Satu lagi adalah untuk mengawal kos, kerana kos ujian ATE agak tinggi. Ujian SLT meletakkan cip pada papan ujian, yang boleh digunakan untuk mengesahkan pelbagai fungsi cip. Kerana mereka mengawal berbilang mesin ujian, ujian kelompok boleh dicapai.

Peralatan perkakasan yang diperlukan untuk ujian SLT termasuk papan ujian, soket ujian, Pengendali, Kit Tukar, hos ujian dan kabel. Ujian SLT adalah ujian tersuai, bahagian perisian mempunyai fleksibiliti yang tinggi, tidak perlu dibangunkan berdasarkan platform ujian automatik, dibangunkan sepenuhnya oleh jurutera ujian. Ujian SLT biasanya termasuk ujian fungsi cip, ujian antara muka berkelajuan tinggi dan ujian berkaitan memori DDR. sama seperti ujian FT, program ini secara fizikal akan membuang cip mengikut keputusan ujian Lulus atau Gagal.

Sebagai tambahan kepada tiga ujian utama di atas, beberapa cip juga mungkin menjalani beberapa ujian kebolehpercayaan, termasuk yang berikut:

1, ESD:ujian imuniti elektrostatik

2, Lateh naik:ujian selak

3, HTOL: ujian hayat kerja suhu tinggi

4, LTOL: ujian hayat kerja suhu rendah

5. TCT:ujian kitaran suhu

6. HAST: ujian tekanan suhu dan kelembapan dipercepatkan tinggi

7, Ujian lain untuk keperluan khas

Peralatan ujian

Ujian cip adalah kompleks, dan ia adalah perkara pengeluaran besar-besaran, jadi ujian automatik berskala besar adalah satu-satunya penyelesaian, dan ujian manual atau bangku tidak dapat menyelesaikan tugas sedemikian. Dalam ujian semikonduktor, mesin ujian, penyusun dan stesen probe adalah tiga peranti utama yang berfungsi bersama untuk memastikan ketepatan dan kecekapan ujian.

1, Mesin ujian

Mesin ujian adalah salah satu peralatan teras ujian semikonduktor. Ia menyediakan fungsi seperti bekalan kuasa, instrumen dan pemprosesan isyarat untuk menguji ciri elektrik dan mengesahkan fungsi cip. Mesin ujian biasanya mempunyai berbilang slot untuk memasukkan cip yang akan diuji. Mengikut keperluan ujian yang berbeza, mesin ujian boleh menjalankan pelbagai ujian voltan, arus, kuasa, kekerapan, pemasaan. Ia boleh melaksanakan prosedur ujian secara automatik dan menjana laporan ujian dan keputusan analisis data.

Teknologi utama penguji termasuk pembangunan program ujian, pendawaian titik ujian, pemerolehan dan pemprosesan isyarat. Untuk meningkatkan kecekapan dan ketepatan ujian, mesin ujian biasanya dilengkapi dengan pemproses isyarat digital berkelajuan tinggi, penukar analog, pengurusan jam teknologi canggih. Di samping itu, mesin ujian juga perlu mempunyai fleksibiliti dan skalabiliti yang baik untuk menyesuaikan diri dengan perubahan dalam jenis cip yang berbeza dan keperluan ujian.

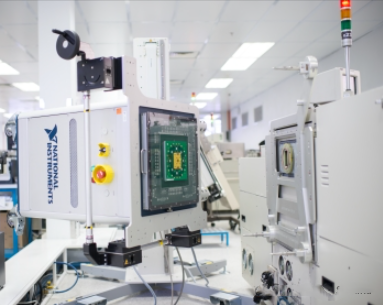

Pada masa ini, syarikat ATE (Automatic Test Equipment) terbesar ialah Teradyne dan Advantest, NI sedang melakukan ini, dan banyak syarikat kecil menggunakan instrumen NI. Syarikat domestik adalah teknologi terkenal Changchuan, Jin Haitong dan sebagainya.

2,Smesin orting

Mesin pengisihan adalah satu lagi peranti penting dalam ujian semikonduktor. Ia digunakan terutamanya untuk mengklasifikasikan dan menyusun cip di bawah ujian mengikut piawaian atau keperluan tertentu. Mesin pengisihan biasanya mempunyai teknologi pemprosesan dan pengecaman imej berkelajuan tinggi, yang boleh menjalankan pengesanan optik dan resolusi cip, dan menilai kualiti dan kesesuaiannya.

Teknologi utama mesin pengisihan termasuk sensor imej, algoritma pemprosesan imej, sistem kawalan gerakan. Melalui pemeriksaan optik dan pemprosesan imej, mesin pengisih boleh mengenal pasti dan mengklasifikasikan cip dengan cepat dan tepat, memilih produk yang tidak layak dan memastikan bahawa hanya cip berkualiti tinggi mengalir ke peringkat pengeluaran seterusnya. Kecekapan tinggi dan ketepatan mesin pengisih adalah sangat penting untuk meningkatkan kecekapan pengeluaran dan mengurangkan kadar produk yang rosak.

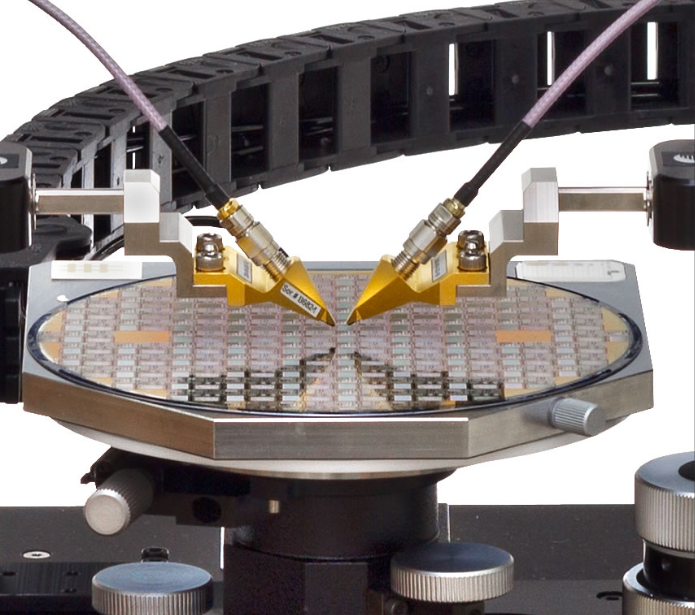

3, Pstesen jubah

Stesen probe adalah salah satu peralatan utama yang digunakan dalam ujian cip. Ia menyediakan platform untuk membetulkan dan menyokong probe ujian, memastikan bahawa probe boleh mencapai titik ujian pada cip secara stabil. Fungsi utama stesen siasatan adalah untuk menyediakan struktur mekanikal yang stabil, penetapan probe yang boleh dipercayai dan penalaan halus, kekonduksian elektrik yang baik dan ciri-ciri penebat.

Teknologi utama stesen probe termasuk reka bentuk struktur mekanikal, penetapan probe dan mekanisme penalaan halus, pemilihan dan rawatan bahan konduktif. Dengan mengawal kedudukan dan tekanan probe dengan tepat, stesen probe dapat memastikan hubungan yang baik antara probe dan cip dan menyediakan persekitaran ujian yang stabil. Ketepatan tinggi dan kestabilan stesen probe memainkan peranan penting dalam ketepatan dan kebolehpercayaan keputusan ujian.

Fountyl Technologies PTE Ltd, memberi tumpuan kepada industri pembuatan semikonduktor, produk utama termasuk: Pin chuck, poros ceramic chuck, seramik end effector, seramik square rasuk, seramik spindle, dialu-alukan untuk menghubungi dan rundingan!