Przemysł chipowy. Terminy techniczne i skróty. Analiza graficzna rzeczowników

Produkcja

TAPEOUT(TO): Oznacza przesłanie ostatecznego pliku GDSII do Foundry w celu przetworzenia.

PEŁNA MASKA: Oznacza to, że wszystkie maski w procesie produkcyjnym służą określonemu projektowi.

MPW (wafel wieloprojektowy):Oznacza to, że wiele projektów korzysta z tego samego płytki, co oznacza, że w tym samym procesie produkcyjnym można wykonać zadanie produkcyjne wielu projektów układów scalonych.

MPW ma dzielić się płytką MASK z innymi producentami, a FULL MASK ma cieszyć się płytką maskującą w pojedynkę. Jeśli ryzyko odprysków jest stosunkowo wysokie, możesz najpierw wykonać MPW, jeśli badanie nie stanowi problemu, a następnie wykonać PEŁNĄ MASKĘ.

Odlewnia:Specjalizujemy się u producentów chipów, takich jak Taiwan Semiconductor Manufacturing (TSMC), Semiconductor Manufacturing International (SMIC), United Electric (UMC). Odpowiednik jest bezfabrykowy, jest producentem projektu, po prostu nie ma fabryk.

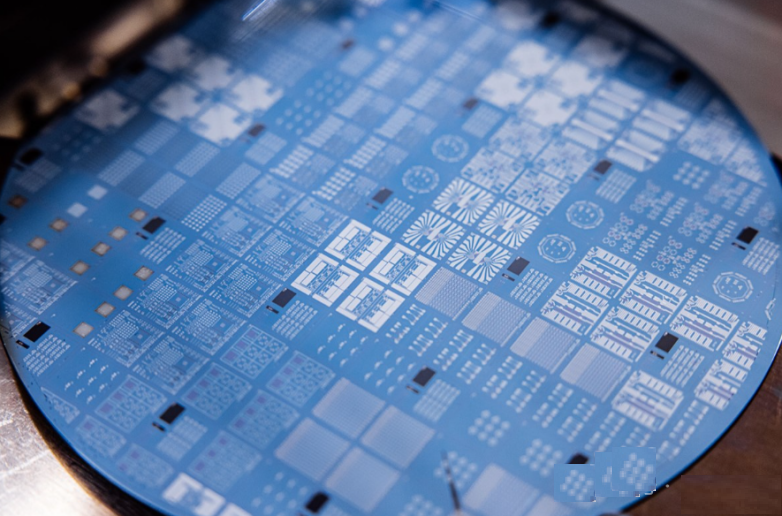

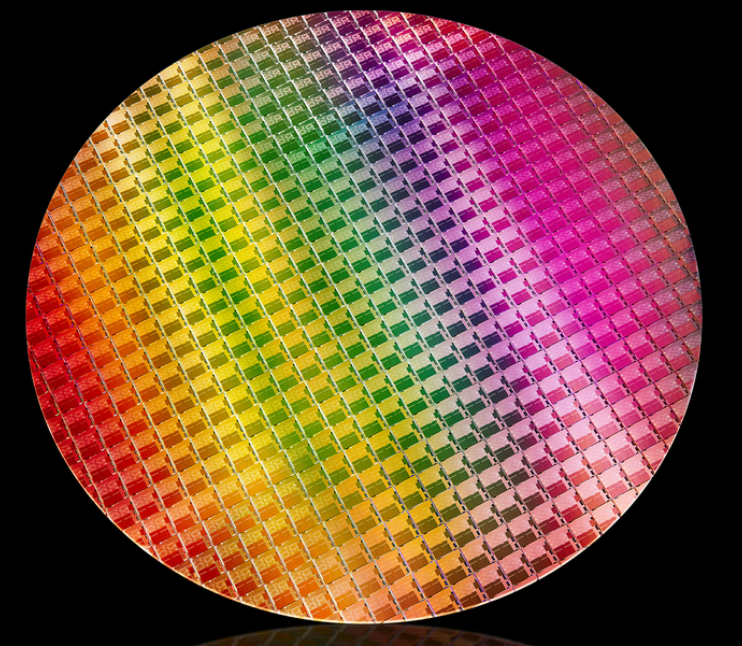

Opłatek

:Po pocięciu wafla powstaje pojedynczy chip, który musi mieć szczelną otoczkę, aby stał się chipem.

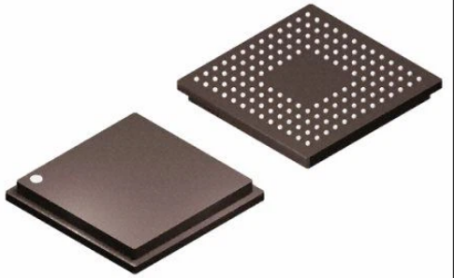

Żeton:Ostateczny pakiet chipa

Uderzenie: zderzenie odnosi się do punktów zderzenia. Po tym, jak wypukły punkt (złoto, cyna ołowiowa, bezołowiowa... itp.) zostanie wyhodowany na powierzchni płytki (przeważnie stosowany w opakowaniu typu flip, czyli flipchip).

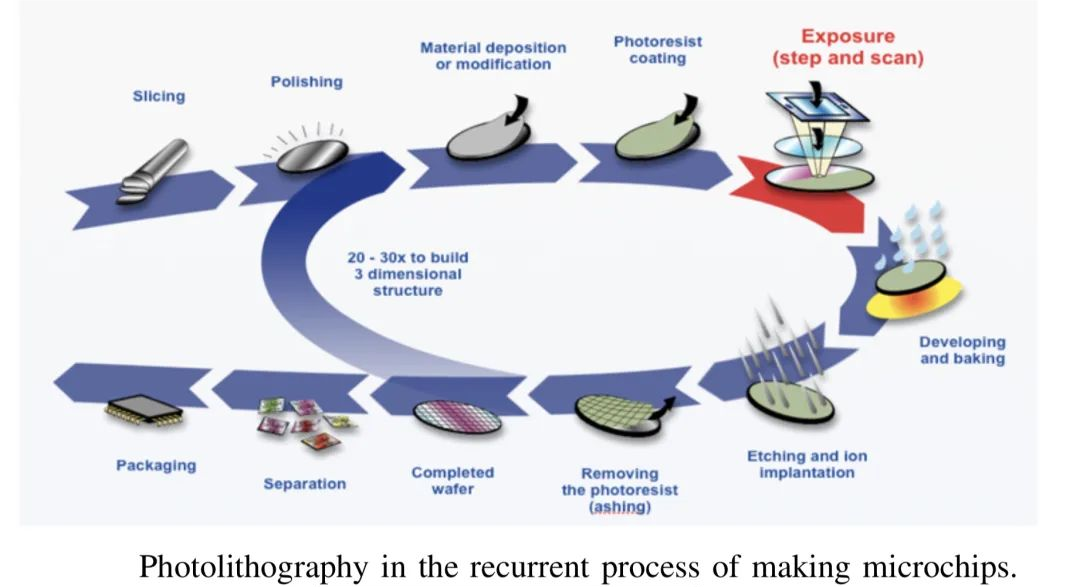

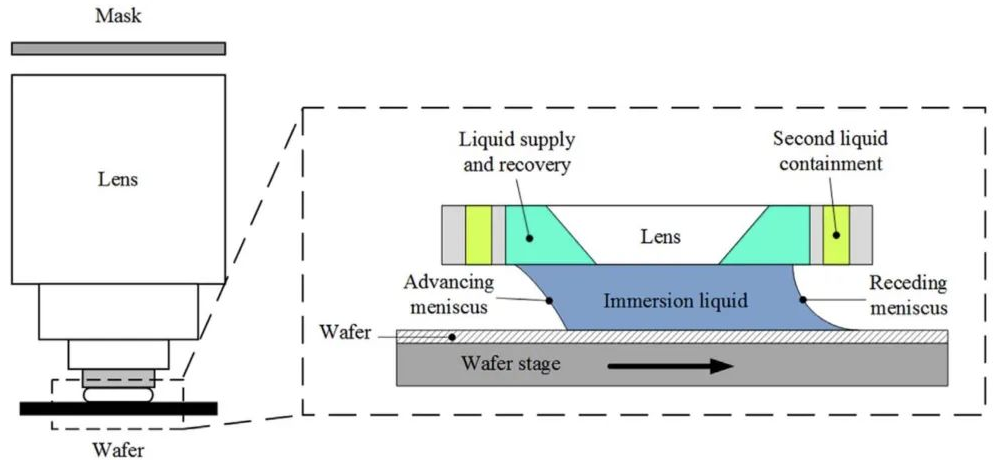

Maska: Zamaskuj nieprzezroczysty szablon graficzny w wybranym obszarze płytki, a późniejsza korozja lub dyfuzja będzie miała wpływ tylko na obszar poza wybranym obszarem

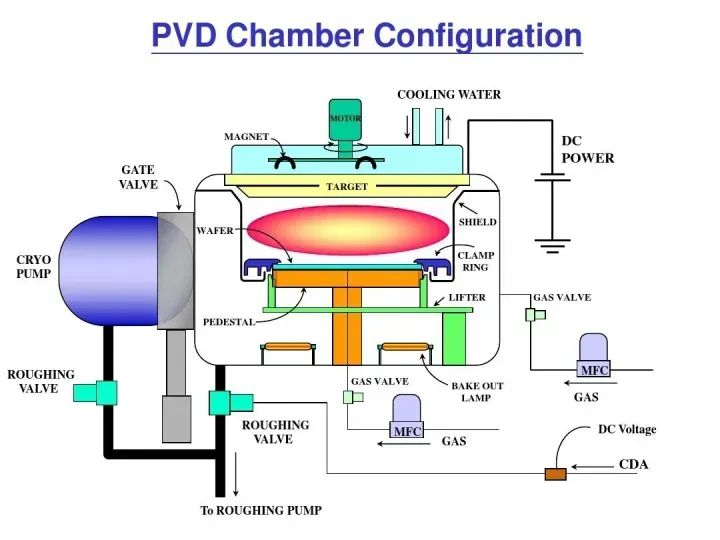

Komora: odnosi się do zamkniętej przestrzeni i ma specjalne przeznaczenie, takie jak odkurzanie, reakcja gazowa lub napylanie metaliczne.

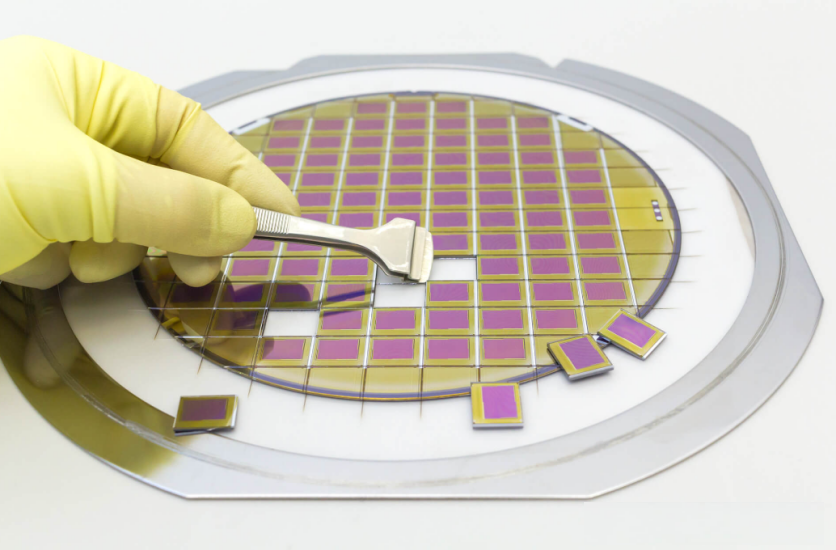

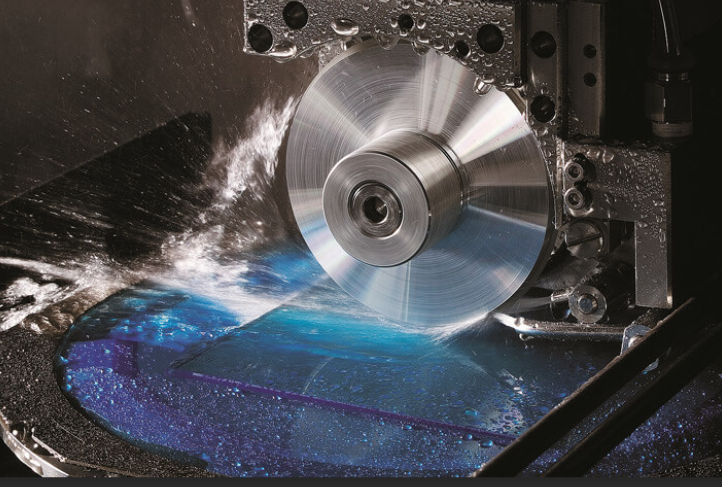

Krojenie wafla: Wafelekkrojenie w kostkę, krojenie wafli

CVD (chemiczne osadzanie z fazy gazowej): jest to zaawansowana technologia szeroko stosowana w dziedzinie przygotowania materiałów, wykorzystująca środowiska o wysokiej temperaturze i niskim ciśnieniu do przekształcania substancji chemicznych w gazach lub mieszaninach gazów w materiały stałe.

PVD (fizyczne osadzanie z fazy gazowej): Metoda mocowania innego materiału do powierzchni podłoża za pomocą technologii plazmy jonowej. To ogólna nazwa sprayu, parowania...etc.

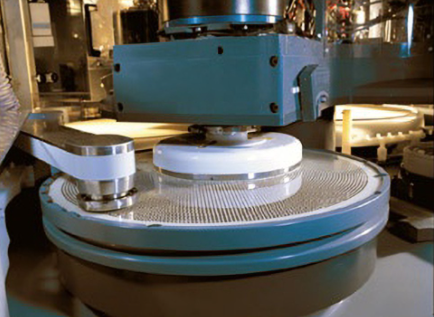

CMP (Polski chemiczno-mechaniczny): Tzastosowanie podkładki szlifierskiej (polerskiej) pokrytej na powierzchni cząstkami ściernymi, za pomocą dodatków chemicznych (odczynnika), w wyniku reakcji chemicznej i szlifowania mechanicznego o podwójnym działaniu, w celu przeprowadzenia obróbki płaskości jej powierzchni na nierównej powierzchni kryształu .

CDA (czyste, suche powietrze): Zwykle odnosi się do powietrza o ciśnieniu od 60 do 110 psi, które zostało oczyszczone i wysuszone. Jako źródło gazu do elementów pneumatycznych.

Dyfuzja: W przemyśle półprzewodników jest często stosowana jako źródło dyfuzji na bardzo czystym chipie krzemowym poprzez wstępne ustawienie lub implantację jonów, a dyfuzja kończy się w ciągu kilku godzin poprzez dodanie wysokiej temperatury do rury pieca

Woda DI: Woda wodociągowa lub woda gruntowa, zawierająca dużą liczbę bakterii, jonów metali i cząstek, musi zostać wysterylizowana i oczyszczona za pomocą sprzętu, a następnie usunięte zanieczyszczenia w postaci jonów metali. Woda pochodna nazywana jest „wodą dejonizowaną”. Zaprojektowany do produkcji układów scalonych.

Domieszka: W oryginalnym materiale półprzewodnikowym aktywna implantacja lub włączenie innych atomów lub jonów na drodze dyfuzji w celu zmiany jego właściwości elektrycznych.

Atrapa wafla: Wafel krzemowy, który pełni w procesie pewną rolę pomocniczą, odróżniając go od produktów. Generalnie wymagania jakościowe nie są zbyt wysokie.

Projekt

Fabless: to połączenie wytwarzania i mniej, co odnosi się do sposobu działania przy projektowaniu układów scalonych bez „bez działalności produkcyjnej i skupiając się wyłącznie na projektowaniu”. Jest również używany w odniesieniu do firm zajmujących się projektowaniem układów scalonych, które nie posiadają zakładów produkujących chipy.

RTL (Register-Transfer Level): Jest to język opisu sprzętu używany do opisu synchronicznych obwodów cyfrowych.

SDC (Synopsys Design Chip): Projekt zapewnia plik ograniczeń, którego potrzebuje narzędzie do syntezy, aby przekonwertować RTL na listę sieci. Główny opis SDC obejmuje: częstotliwość pracy chipa, taktowanie IO chipa, zasady projektowania, ścieżki specjalne, ścieżki bez kontroli i tak dalej.

Weryfikacja funkcji chipa: Dotyczy głównie metodologii weryfikacji chipa, sprawdzającej, czy RTL i model referencyjny są spójne.

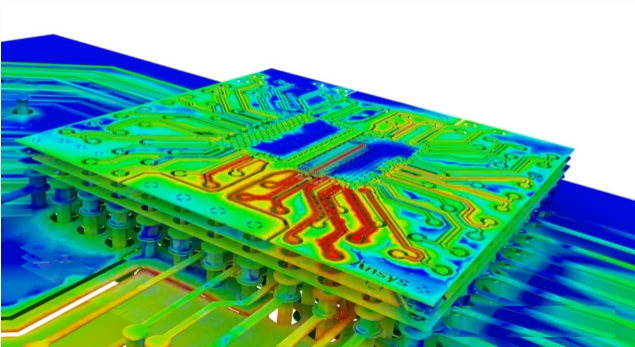

Symulacja: symulacja to zazwyczaj generowany przebieg, ogólnie funkcje chipa, weryfikacja, zużycie energii chipa, można symulować, bardziej intuicyjne odzwierciedlenie rzeczywistej sceny.

IP (własność intelektualna): zasoby projektowe, funkcjonalne moduły obwodów (rdzenie, jednostki), które zostały zaprojektowane

DesignRule: Ponieważ technologia procesów półprzewodnikowych jest technologią profesjonalną, delikatną i złożoną, podatną na wpływ różnych metod procesowych sprzętu produkcyjnego (RECIPE), konieczne jest posiadanie zestawu specyfikacji w celu utworzenia rezerw technicznych przy rozważaniu sposobu zaangażowania się w technologię produkcyjną perfekcja i udane wytwarzanie różnorodnych produktów, czyli „DesignRule”. Jest formułowany zgodnie z wymaganiami, specyfikacjami, sprzętem produkcyjnym i metodami procesu, możliwościami procesu i powiązanymi parametrami elektrycznymi różnych produktów.

TEST

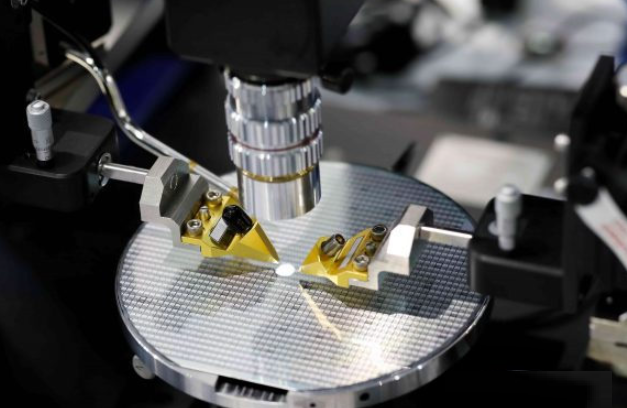

CP (Chip Probing): Przetestuj bezpośrednio płytkę, a obiektem testu jest każda matryca w całej płytce. Celem jest upewnienie się, że każda matryca w całej płytce może zasadniczo spełniać charakterystykę urządzenia lub specyfikacje projektowe, zwykle łącznie z weryfikacją dla napięcia, prądu, taktowania i funkcji. Można go wykorzystać do testowania poziomu procesu produkcyjnego w fabrykach.

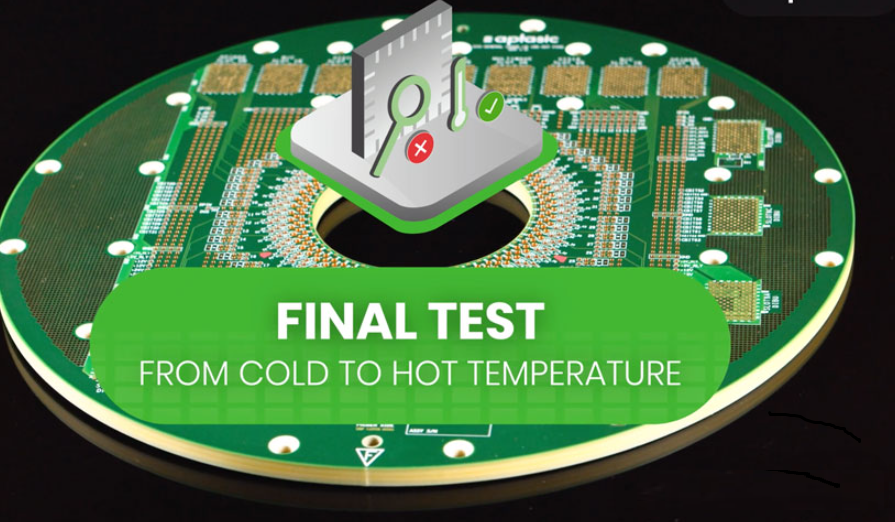

FT (test końcowy): To ostatni przechwyt, zanim chip opuści fabrykę. Obiekt testowy dotyczy kapsułkowanego chipa, który zostanie hermetyzowany po teście CP, a następnie teście FT po enkapsulacji. Można go wykorzystać do sprawdzenia poziomu technicznego linii pakującej.

CP za wafelek, jeśli zła matryca nie wymaga pakowania, oszczędzając koszty pakowania i koszty podłoża.

Po zakończeniu testu CP w procesie pakowania zostanie wprowadzona awaria chipa, dlatego do usunięcia uszkodzonego chipa potrzebna jest również FT.

Wydajność: wydajność chipa jest związana z procesem, chip ma pewne prawdopodobieństwo awarii, a im większy chip, tym większe prawdopodobieństwo awarii.

IP (własność intelektualna):W projektowaniu układów scalonych kompletny moduł funkcjonalny sprawdzonego układu scalonego wielokrotnego użytku o określonej funkcji.

Asortyment IP można podzielić na Licencje, Lojalność ze względu na sposób pobierania opłat

licencja Autoryzacja Licencja: zezwolenie na korzystanie z tego adresu IP, autoryzacja adresu IP.

Opłaty za lojalność: gdy użytkownik wykorzysta adres IP, naliczane są za każdy chip.

IP to podstawowy element chipa, taki jak USB, PCIE, procesor to IP, cały chip jest zintegrowany z IP, chip może wykonywać bardziej złożone zadania, rdzeniem jest ponowne wykorzystanie IP. Na przykład w przypadku tych, które wytwarzają dziesiątki milionów, setki milionów drzwi, można ponownie wykorzystać własność intelektualną.

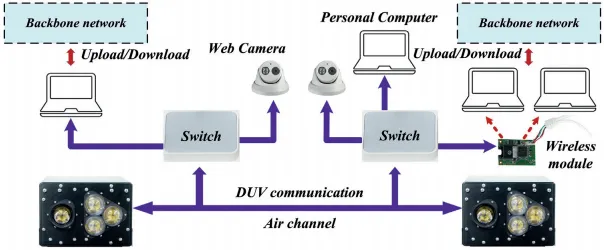

DUV (promienie głębokiego ultrafioletu) EUV (promienie ekstremalnego ultrafioletu)

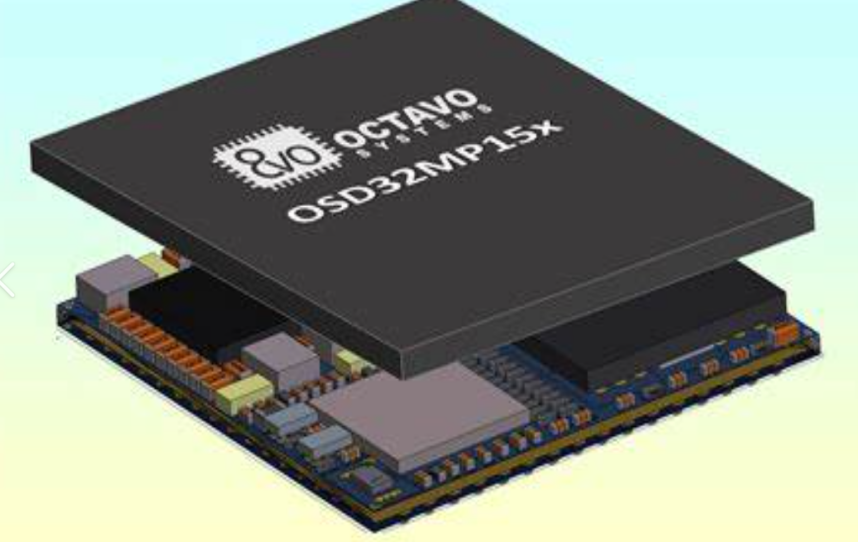

Opakowanie

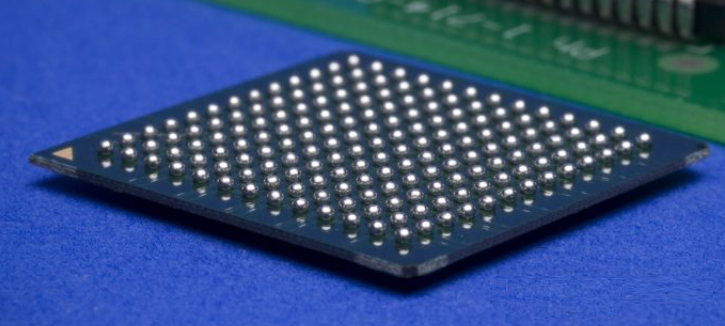

BGA (Ball Grid Array): rodzaj obudowy do montażu powierzchniowego, w której pewna liczba połączonych kulek lutowniczych jest rozmieszczonych na podłożu osadzonym na chipie (matryca kulek).

ASIC (układ scalony specyficzny dla aplikacji): ASIC to specjalny układ scalony, będący ogólnym terminem określającym układ scalony specjalnie dostosowany do konkretnych potrzeb. Na przykład dedykowane procesory audio i wideo, a obecnie wiele dedykowanych chipów AI, można uznać za rodzaj ASIC.

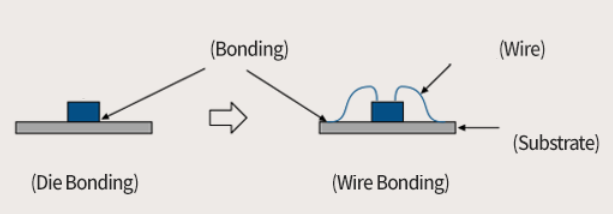

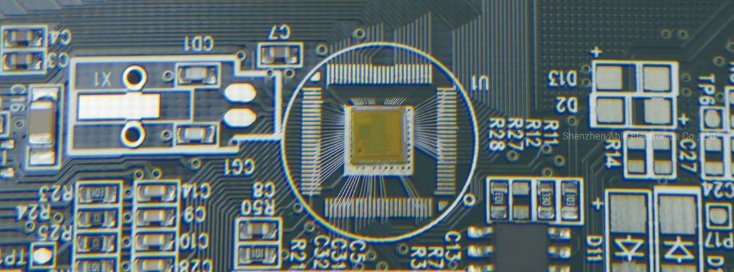

Łączenie drutu: Łączenie drutu (zgrzewanie, znane również jako wiązanie, klejenie, spawanie drutem) odnosi się do użycia drutu metalowego (drutu złotego, drutu aluminiowego itp.), zastosowania prasowania na gorąco lub energii ultradźwiękowej w celu zakończenia połączenia wewnętrznego okablowania obwodu półprzewodnikowego, to znaczy połączenia między chipem a obwodem lub ramką prowadzącą.

Umrzeć związany:

Flipchip: kulkę z ołowiu z cyny osadza się na I/Opad, a następnie chip odwraca się i podgrzewa za pomocą kulki ze stopionego ołowiu z cyny połączonej z podłożem ceramicznym.

COB (chip na płycie): Wbudowane opakowanie chipa polega na przymocowaniu gołego chipa do płytki PCB za pomocą przewodzącego lub nieprzewodzącego kleju, a następnie wykonaniu łączenia przewodów w celu uzyskania połączenia elektrycznego, a następnie owinięciu chipa i połączenia przewodu za pomocą spoiwo.

SOC (System On Chip): polega na umieszczeniu procesora, magistrali, urządzeń peryferyjnych... itp. w wewnętrznej implementacji chipa. Na przykład procesor telefonu komórkowego to złożony układ SOC.

SIP (system w pakiecie): Pakiet SiP to surowy układ z różnymi funkcjami, w tym procesorem, procesorem graficznym, pamięcią... itd. zintegrowane w korpusie opakowania, tak aby uzyskać cały system chipów.

SOP (mały pakiet konspektu): mały zewnętrzny pakiet pakietów układów scalonych, w którym przewody są ciągnięte w obu kierunkach

DAF (Die Apply Film): Technologia klejenia folii waflowej

CMOS (komplementarny półprzewodnik z tlenkiem metalu): uzupełniający półprzewodnik z tlenku metalu. Odnosi się do technologii stosowanej do wytwarzania wielkoskalowych układów scalonych lub układów scalonych wykonanych przy użyciu tej technologii, czyli fragmentu układu pamięci RAM, który można odczytywać i zapisywać na płycie głównej komputera. Ze względu na właściwości odczytu i zapisu służy do zapisywania danych BIOS-u po ustawieniu parametrów sprzętowych komputera na płycie głównej komputera, a układ ten służy wyłącznie do przechowywania danych.

JEDEC (Standardy Joint Electron Device Engineering Council): amerykańskie specyfikacje standardowe dotyczące wymiarów opakowania.

Fountyl Technologies PTE Ltd koncentruje się na przemyśle produkcji półprzewodników, a główne produkty to: uchwyt kołkowy, porowaty uchwyt ceramiczny, ceramiczny efektor końcowy, ceramiczna belka kwadratowa, wrzeciono ceramiczne, zapraszamy do kontaktu i negocjacji!