Como resolver o problema de dissipação de calor do pacote de chips

Os chips de embalagens avançadas podem não apenas atender às necessidades de computação de alto desempenho, inteligência artificial, crescimento da densidade de potência, etc., mas também o problema de dissipação de calor das embalagens avançadas se tornou complicado. Porque os pontos quentes em um chip afetam a distribuição de calor dos chips vizinhos. As interconexões entre chips também são mais lentas em módulos do que em SoCs.

John Parry, chefe da indústria de eletrônicos e semicondutores da Siemens Digital Industry Software, disse: "Antes de o mundo mudar para áreas como multi-core, você estava lidando com um chip que tinha uma potência máxima de cerca de 150 watts por centímetro quadrado, que era uma fonte de calor de ponto único Você pode dissipar o calor em todas as três direções, para obter densidades de potência bastante altas. Mas quando você tem um chip, coloque outro chip próximo a ele e, em seguida, coloque outro chip próximo a ele, eles aquecem. uns aos outros. Isso significa que você não pode tolerar que cada chip tenha o mesmo nível de potência, o que torna o desafio térmico muito mais difícil."

Esta é uma das principais razões pelas quais o empilhamento 3D-IC está progredindo lentamente no mercado. Embora o conceito faça sentido do ponto de vista de eficiência energética e integração - e funcione bem em 3D NAND e HBM - a história é diferente quando a lógica é incluída. O chip lógico gera calor, e quanto mais densa a lógica, maior a utilização dos elementos de processamento, maior o calor. Isso torna o empilhamento lógico raro.

Escolha o pacote certo

Para designers de chips, há muitas maneiras de empacotar. Mas o desempenho da integração de chips é crucial. Componentes como colunas de silício, TSV e cobre têm diferentes coeficientes de expansão térmica (TCE), o que afeta o rendimento da montagem e a confiabilidade a longo prazo.

O popular pacote flip BGA atual com CPU e HBM tem uma área de cerca de 2.500 milímetros quadrados. Mike McIntyre, chefe de gerenciamento de produtos de software da Onto Innovation, disse: “Estamos vendo um chip grande potencialmente se transformando em quatro ou cinco chips pequenos. Assim, você pode distribuir o calor. Em última análise, a dissipação de calor é um problema que só pode ser resolvido no nível do sistema e apresenta uma série de compensações.

Na verdade, alguns dispositivos são tão complexos que é difícil substituir facilmente componentes para personalizar esses dispositivos para aplicações em campos específicos. É por isso que muitos produtos de embalagens avançadas são para componentes de volume muito alto ou com preços elásticos, como chips de servidor.

Progresso na simulação e teste de módulos de chip

No entanto, os engenheiros estão procurando novas maneiras de realizar análises térmicas de confiabilidade do pacote antes que os módulos embalados sejam fabricados. Por exemplo, a Siemens fornece um exemplo de módulo duplo baseado em ASIC que instala uma camada de redistribuição fan-out (RDL) em um substrato orgânico multicamadas em um pacote BGA. Ele usa dois modelos, um para WLP baseado em RDL e outro para substrato orgânico multicamadas BGA. Esses modelos de embalagem são parametrizados, incluem empilhamento de substrato e BGA antes que as informações do EDA sejam introduzidas e permitem a avaliação antecipada do material e a seleção do posicionamento do chip. Em seguida, os dados EDA são importados e, para cada modelo, o mapa de materiais é capaz de fornecer uma descrição térmica detalhada da distribuição do cobre em todas as camadas.

Eric Ouyang, Diretor de Marketing Técnico da JCET, juntamente com engenheiros da JCET e Meta, compararam o desempenho térmico de módulos de chip único, módulos multichip, plugboards 2,5D e chips empilhados 3D com um ASIC e dois Srams. [1] A comparação entre Apple deixa o ambiente de servidor, radiador com câmara de vácuo e TIM inalterados. Em termos de calor, 2,5D e MCM têm desempenho melhor do que chips 3D ou de chip único.

Resistência térmica quantizada

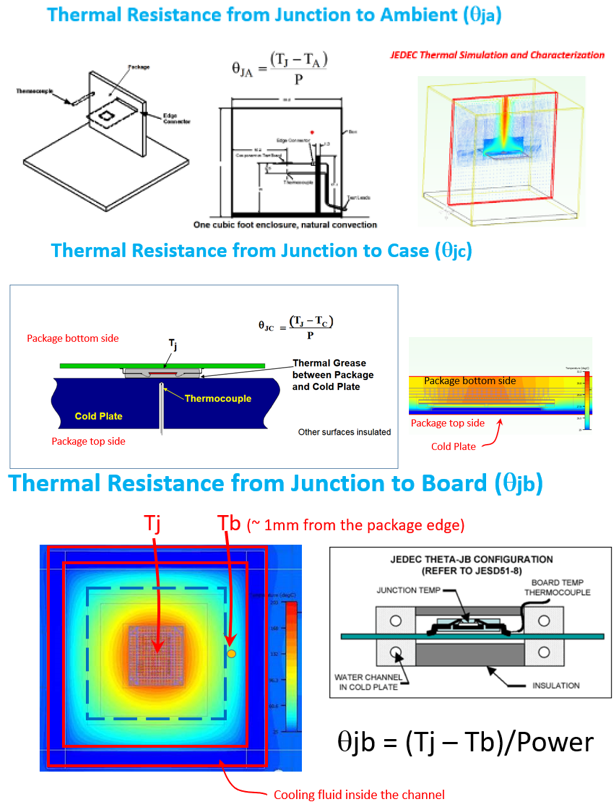

Podemos entender como o calor é conduzido através de chips de silício, placas de circuito, colas, TIMs ou tampas de embalagens, enquanto usamos o método padrão de diferença de temperatura e função de potência para rastrear valores de temperatura e resistência.

"O caminho térmico é quantificado por três valores principais - a resistência térmica do nó do dispositivo ao ambiente, a resistência térmica do nó ao invólucro [na parte superior do pacote] e a resistência térmica do nó à placa ”, diz Ouyang do JCET. No mínimo, ressalta ele, os clientes do JCET precisam de ɵja, ɵjc e ɵjb, que eles usam no projeto do sistema. Eles podem exigir que uma determinada resistência térmica não exceda um valor específico e que o design da embalagem proporcione esse desempenho.

A simulação térmica é a forma mais econômica de explorar a seleção e colocação de materiais. Através da simulação do chip em estado de funcionamento, normalmente encontramos um ou mais pontos quentes, para que possamos adicionar cobre ao substrato abaixo do ponto quente para facilitar a dissipação de calor; Ou troque o material da embalagem, aumente o radiador. O integrador do sistema pode especificar que a resistência térmica ɵja, ɵjc e ɵjb não deve exceder determinados valores. Em circunstâncias normais, a temperatura da junção de silício deve ser mantida abaixo de 125 ° C. Após a simulação ser concluída, a fábrica de embalagens conduz um projeto de experimentos (DOE) para chegar ao plano de embalagem final.

Selecione TIM

Na embalagem, mais de 90% do calor é dissipado através da embalagem, do topo do chip até o radiador, que geralmente é uma aleta vertical baseada em alumínio anodizado. Materiais de interface térmica (TIM) com alta condutividade térmica são colocados entre o chip e a embalagem para ajudar na transferência de calor. TIM de próxima geração para cpus inclui ligas de chapa metálica, como índio e estanho, bem como estanho sinterizado com prata com condutividade de 60W/mK e 50W/mK, respectivamente. À medida que os fornecedores fazem a transição de SoCs para processos de chiplet, são necessários mais TIMs com diferentes propriedades e espessuras.

YoungDo Kweon, diretor sênior de pesquisa e desenvolvimento da Amkor, disse que para sistemas de alta densidade, a resistência térmica do TIM entre o chip e o pacote tem um impacto maior na resistência térmica geral do módulo embalado. As tendências de energia estão aumentando dramaticamente, especialmente para lógica, por isso nos concentramos em manter a temperatura da junção baixa para garantir uma operação confiável de semicondutores. Embora os fornecedores TIM forneçam valores de resistência térmica para seus materiais, na realidade, a resistência térmica do chip à embalagem (ɵjc) é afetada pelo próprio processo de montagem, incluindo a qualidade da ligação e a área de contato entre o chip e o TIM. Ele observa que testar com ferramentas de montagem reais e materiais de ligação em um ambiente controlado é fundamental para compreender as propriedades térmicas reais e selecionar o melhor TIM para verificação do cliente.

Para lidar com o calor de maneiras diferentes

Os fabricantes de chips estão procurando maneiras de resolver o problema de dissipação de calor. Randy White, gerente de programa para soluções de memória da Keysight Technologies, disse: "O pacote é o mesmo, se você reduzir a área do tamanho do chip em um quarto, ele irá acelerar. Isso pode resultar em algumas diferenças de integridade do sinal. Porque a linha de ligação do pacote externo entrará no chip, quanto mais longa a linha, maior será a indutância, então há uma parte de desempenho elétrico. Então, como você consome tanta energia em um espaço pequeno o suficiente? estudado." Isto levou a um investimento significativo em pesquisas de ponta sobre ligações que parecem focar em ligações híbridas. Mas o custo da ligação híbrida é elevado e ainda está limitado a aplicações do tipo processador de alto desempenho, sendo a TSMC uma das únicas empresas que oferece atualmente esta tecnologia. No entanto, a perspectiva de combinar fótons em chips CMOS ou nitreto de gálio à base de silício é muito promissora.

Fountyl Technologies PTE Ltd, está se concentrando na indústria de fabricação de semicondutores, os principais produtos incluem: mandril de pino, mandril de cerâmica porosa, efetor final de cerâmica, viga quadrada de cerâmica, fuso de cerâmica, bem-vindo ao contato e negociação!