อุตสาหกรรมชิป ศัพท์เทคนิคและคำย่อ การวิเคราะห์คำนามเชิงกราฟิก

การผลิต

TAPEOUT (TO): หมายถึงการส่งไฟล์ GDSII สุดท้ายไปยัง Foundry เพื่อดำเนินการ

หน้ากากแบบเต็ม: นั่นคือ หน้ากากทั้งหมดในกระบวนการผลิตมีการออกแบบบางอย่าง

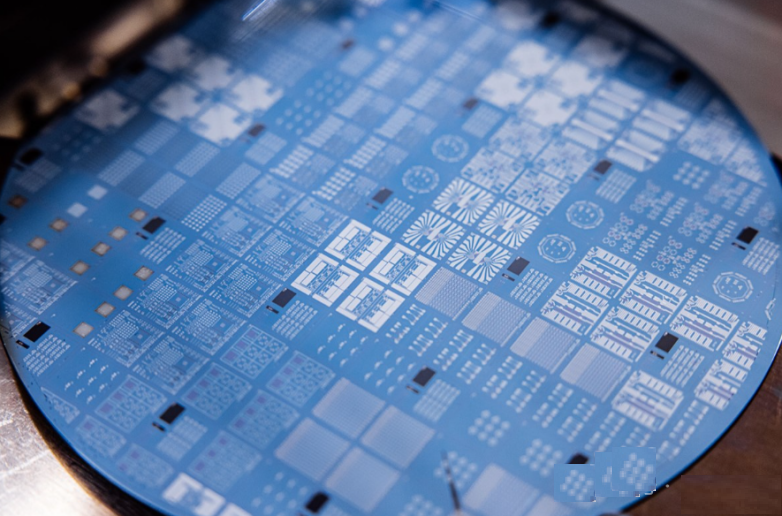

MPW (เวเฟอร์หลายโครงการ):กล่าวคือ หลายโครงการใช้เวเฟอร์ร่วมกัน กล่าวคือ กระบวนการผลิตเดียวกันสามารถรองรับงานการผลิตที่มีการออกแบบ IC หลายแบบได้

MPW คือการแบ่งปันแผ่น MASK กับผู้ผลิตรายอื่น และ FULL MASK คือการใช้แผ่นมาส์กเพียงอย่างเดียว หากความเสี่ยงของเศษค่อนข้างสูง คุณสามารถทำ MPW ก่อน ถ้าการทดสอบไม่มีปัญหา แล้วจึงทำ FULL MASK

โรงหล่อ-เชี่ยวชาญ ed ในผู้ผลิตการผลิตชิป เช่น Taiwan Semiconductor Manufacturing (TSMC), Semiconductor Manufacturing International (SMIC), United Electric (UMC) สิ่งที่เกี่ยวข้องกันคือนิทาน เป็นผู้ผลิตผู้ออกแบบ ไม่ใช่โรงงานผลิต

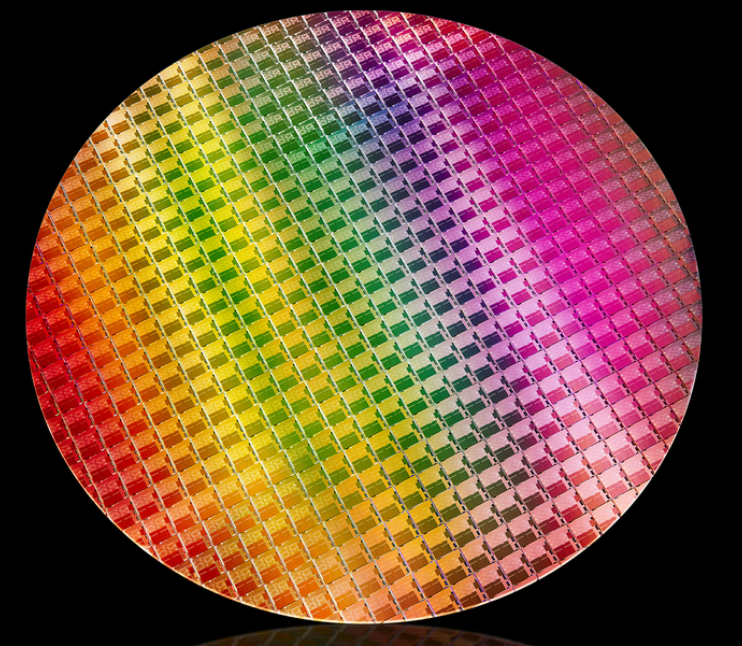

เวเฟอร์

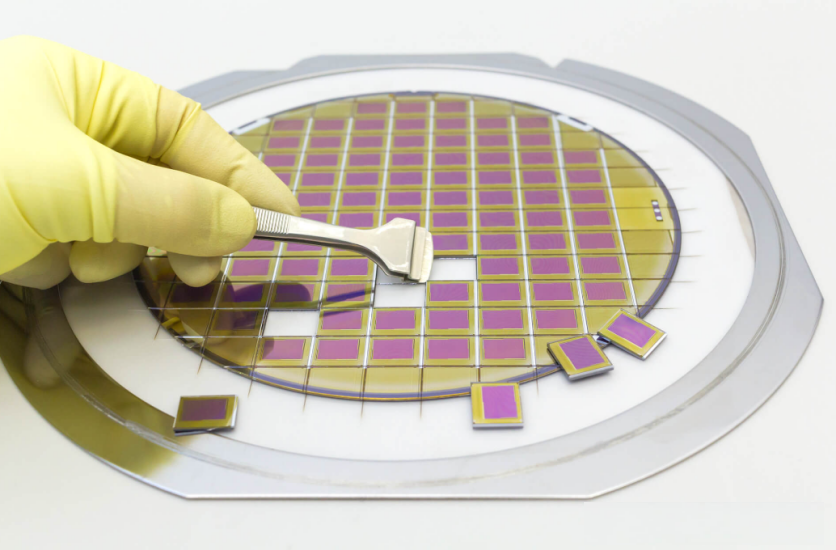

ที่:หลังจากตัดเวเฟอร์แล้ว ก็จะเป็นเวเฟอร์ของชิปตัวเดียวซึ่งต้องเพิ่มเปลือกที่ปิดสนิทจึงจะกลายเป็นชิป

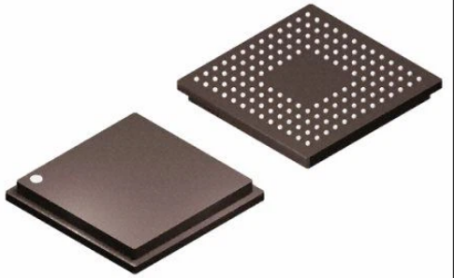

ชิป:แพ็คเกจสุดท้ายของชิป

บั๊ม: การชนหมายถึงจุดชน หลังจากที่จุดนูน (ทอง ตะกั่วดีบุก ไร้สารตะกั่ว...ฯลฯ) เติบโตขึ้นบนพื้นผิวของแผ่นเวเฟอร์ (ส่วนใหญ่ใช้กับแพ็คเกจกระบวนการพลิก นั่นคือฟลิปชิป)

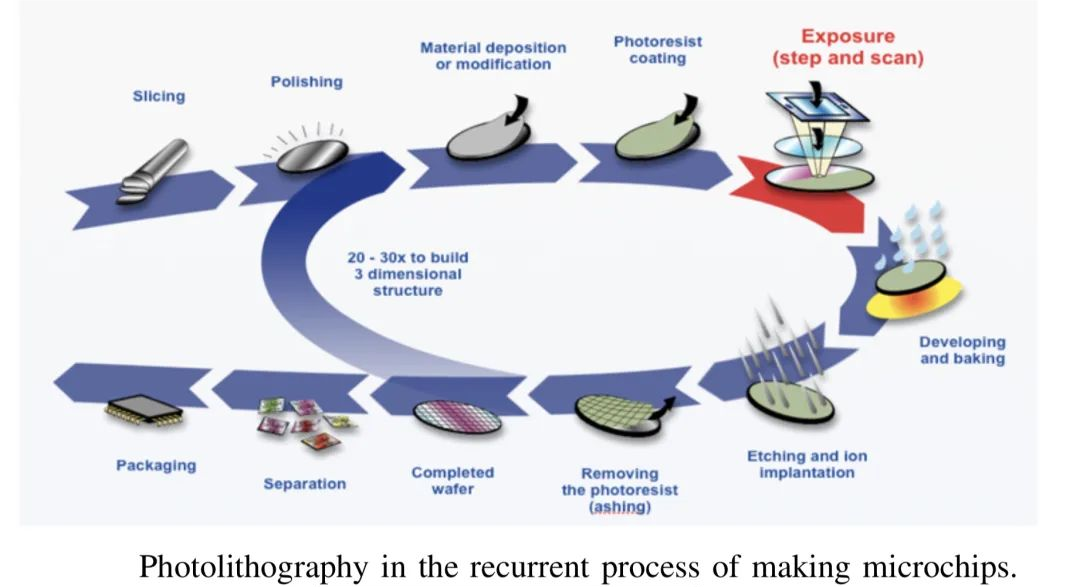

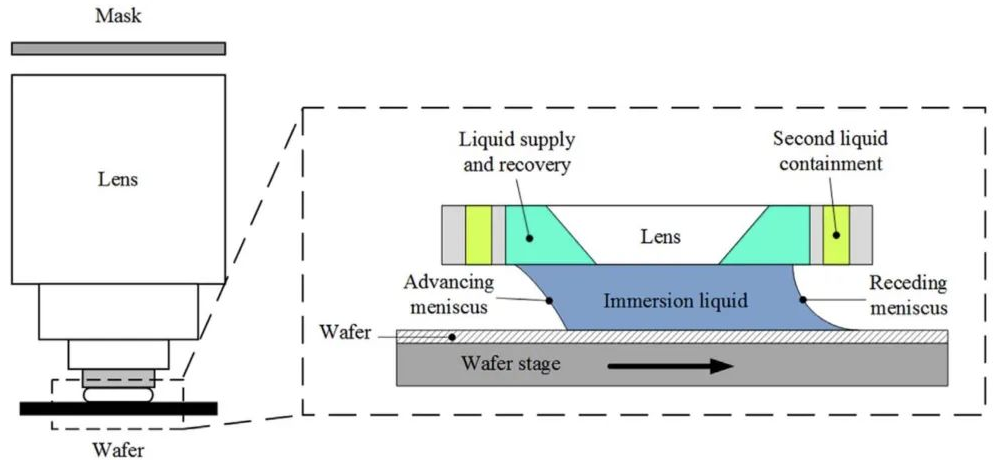

หน้ากาก : ปิดบังเทมเพลตกราฟิกทึบแสงในพื้นที่ที่เลือกบนแผ่นเวเฟอร์ และการกัดกร่อนหรือการแพร่กระจายที่ตามมาจะส่งผลต่อพื้นที่นอกพื้นที่ที่เลือกเท่านั้น

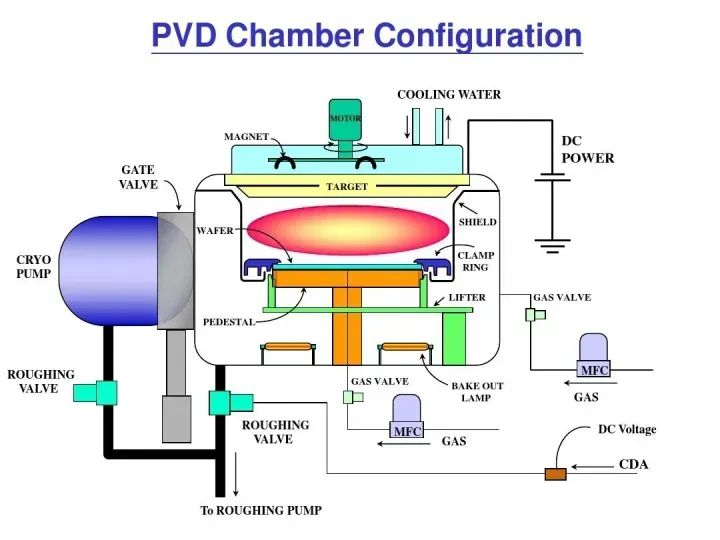

ห้อง:หมายถึงพื้นที่จำกัดและมีวัตถุประสงค์พิเศษ เช่น การดูดฝุ่น ปฏิกิริยาแก๊ส หรือการสปัตเตอร์โลหะ

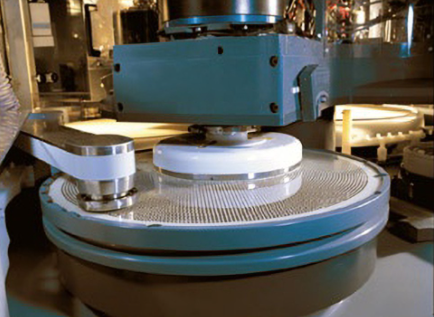

เวเฟอร์หั่นเต๋า:เวเฟอร์หั่นสี่เหลี่ยมลูกเต๋า, การตัดเวเฟอร์

CVD (การสะสมไอสารเคมี): เป็นเทคโนโลยีขั้นสูงที่ใช้กันอย่างแพร่หลายในด้านการเตรียมวัสดุ โดยใช้สภาพแวดล้อมที่มีอุณหภูมิสูงและความดันต่ำในการแปลงสารเคมีในก๊าซหรือส่วนผสมของก๊าซให้เป็นวัสดุแข็ง

PVD (การสะสมไอทางกายภาพ): วิธีการติดวัสดุอื่นเข้ากับพื้นผิวของซับสเตรตด้วยเทคโนโลยีไอออนพลาสมา เป็นชื่อทั่วไปของสเปรย์ การระเหย...ฯลฯ

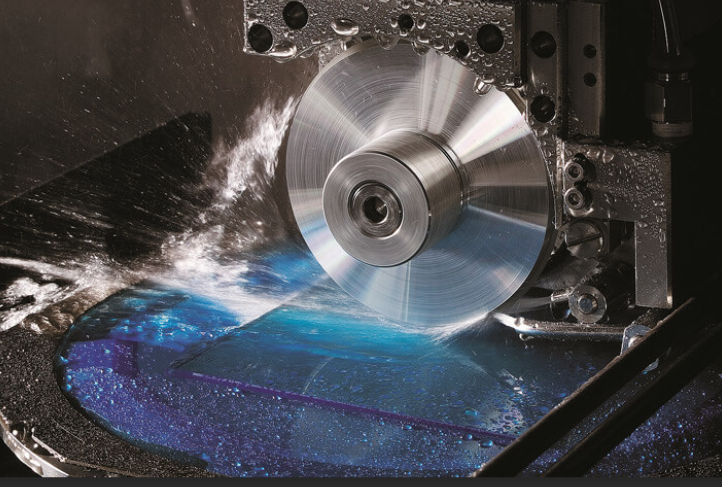

CMP (น้ำยาขัดเงาเคมี-เครื่องกล): Tเขาใช้แผ่นเจียร (แผ่นขัดเงา) ที่ปกคลุมไปด้วยอนุภาคการเจียรบนพื้นผิว ด้วยความช่วยเหลือของสารเคมี (รีเอเจนต์) พร้อมปฏิกิริยาเคมีและการบดเชิงกลของการประมวลผลแบบสองครั้งเพื่อดำเนินการรักษาความเรียบของพื้นผิวบนพื้นผิวคริสตัลที่ไม่สม่ำเสมอ .

CDA (อากาศแห้งที่สะอาด) : โดยทั่วไปหมายถึงอากาศที่มีความดันระหว่าง 60 ถึง 110psi ซึ่งได้รับการทำให้บริสุทธิ์และทำให้แห้งแล้ว เป็นแหล่งก๊าซสำหรับส่วนประกอบเกี่ยวกับนิวแมติก

การแพร่กระจาย: ในอุตสาหกรรมเซมิคอนดักเตอร์มักใช้เป็นแหล่งการแพร่กระจายบนชิปซิลิคอนบริสุทธิ์มากโดยการตั้งค่าล่วงหน้าหรือการฝังไอออน และการแพร่กระจายจะเสร็จสิ้นภายในไม่กี่ชั่วโมงโดยการเพิ่มอุณหภูมิสูงให้กับท่อเตาเผา

น้ำ DI: น้ำประปาหรือน้ำใต้ดินที่มีแบคทีเรีย ไอออนของโลหะ และอนุภาคจำนวนมาก จะต้องผ่านการฆ่าเชื้อและทำให้บริสุทธิ์ด้วยอุปกรณ์ จากนั้นจึงกำจัดสิ่งเจือปนของไอออนของโลหะออก น้ำที่ได้เรียกว่า "น้ำปราศจากไอออน" ออกแบบมาสำหรับการผลิตไอซี

สารเจือปน: ในวัสดุเซมิคอนดักเตอร์ดั้งเดิม การฝังแบบแอคทีฟหรือการรวมตัวกันของอะตอมหรือไอออนอื่น ๆ โดยการแพร่เพื่อเปลี่ยนคุณสมบัติทางไฟฟ้า

Dummy Wafer : เวเฟอร์ซิลิคอนที่มีบทบาทเสริมในกระบวนการนี้ แยกความแตกต่างจากผลิตภัณฑ์ โดยทั่วไปข้อกำหนดด้านคุณภาพไม่สูงมาก

ออกแบบ

Fabless: เป็นการผสมผสานระหว่างการผลิตและการผลิตที่น้อยกว่า ซึ่งหมายถึงโหมดการทำงานของการออกแบบวงจรรวมโดย "ไม่มีธุรกิจการผลิตและมุ่งเน้นเฉพาะการออกแบบ" นอกจากนี้ยังใช้เพื่ออ้างถึงบริษัทออกแบบ IC ที่ไม่มีโรงงานผลิตชิป

RTL (ระดับการลงทะเบียน-ถ่ายโอน): เป็นภาษาคำอธิบายฮาร์ดแวร์ที่ใช้อธิบายวงจรดิจิทัลแบบซิงโครนัส

SDC(Synopsys Design Chip) :การออกแบบให้ไฟล์ข้อจำกัดที่เครื่องมือสังเคราะห์จำเป็นต้องแปลง RTL เป็น netlist คำอธิบายหลักของ SDC ประกอบด้วย: ความถี่ในการทำงานของชิป, ไทม์มิ่งของชิป IO, กฎการออกแบบ, เส้นทางพิเศษ, เส้นทางที่ไม่มีการตรวจสอบ และอื่นๆ

การตรวจสอบการทำงานของชิป: ส่วนใหญ่หมายถึงวิธีการตรวจสอบชิป เพื่อตรวจสอบว่า RTL และโมเดลอ้างอิงสอดคล้องกันหรือไม่

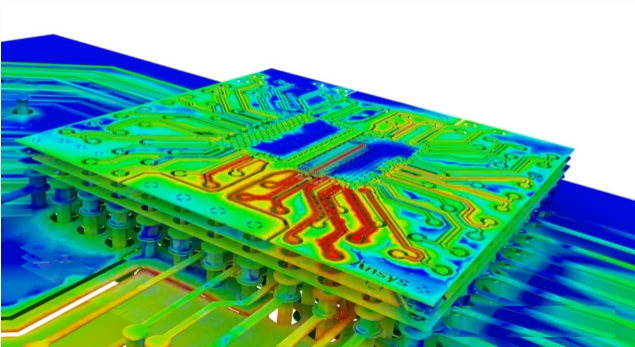

การจำลอง: การจำลองมักจะสร้างรูปคลื่น โดยทั่วไป ฟังก์ชันชิป การตรวจสอบ การใช้พลังงานของชิป สามารถจำลองได้ การสะท้อนฉากจริงได้ง่ายขึ้น

IP (ทรัพย์สินทางปัญญา):สินทรัพย์การออกแบบ โมดูลวงจรการทำงาน (แกน หน่วย) ที่ได้รับการออกแบบ

กฎการออกแบบ:เนื่องจากเทคโนโลยีกระบวนการเซมิคอนดักเตอร์เป็นเทคโนโลยีระดับมืออาชีพ ละเอียดอ่อน และซับซ้อน ซึ่งไวต่ออิทธิพลของวิธีกระบวนการผลิตอุปกรณ์การผลิตที่แตกต่างกัน (RECIPE) จึงจำเป็นต้องมีชุดข้อกำหนดเพื่อทำข้อกำหนดทางเทคนิคเมื่อพิจารณาว่าจะมีส่วนร่วมในเทคโนโลยีการผลิตอย่างไร ความสมบูรณ์แบบและความสำเร็จในการผลิตผลิตภัณฑ์ต่างๆ ซึ่งก็คือ “DesignRule” ได้รับการกำหนดสูตรตามข้อกำหนด ข้อมูลจำเพาะ อุปกรณ์การผลิตและวิธีการของกระบวนการ ความสามารถของกระบวนการ และพารามิเตอร์ทางไฟฟ้าที่เกี่ยวข้องของผลิตภัณฑ์ต่างๆ

ทดสอบ

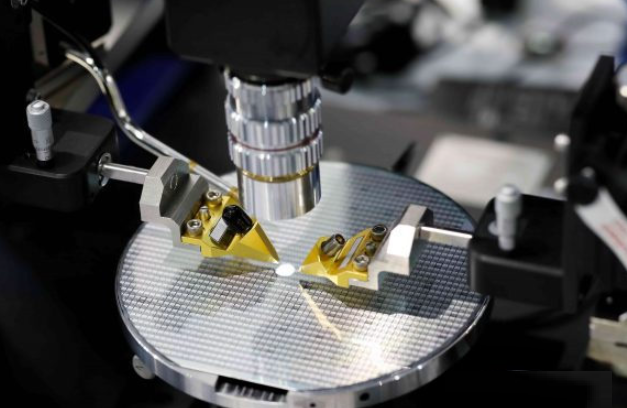

CP (Chip Probing): ทดสอบเวเฟอร์โดยตรง และวัตถุทดสอบมีไว้สำหรับ Die แต่ละตัวในเวเฟอร์ทั้งหมด จุดประสงค์คือเพื่อให้แน่ใจว่า Die แต่ละตัวในเวเฟอร์ทั้งหมดโดยทั่วไปจะมีคุณสมบัติตรงตามลักษณะของอุปกรณ์หรือข้อกำหนดการออกแบบ โดยปกติจะรวมถึงการตรวจสอบด้วย สำหรับแรงดันไฟฟ้า กระแส เวลา และฟังก์ชัน สามารถใช้ทดสอบระดับกระบวนการผลิตในโรงงาน fab ได้

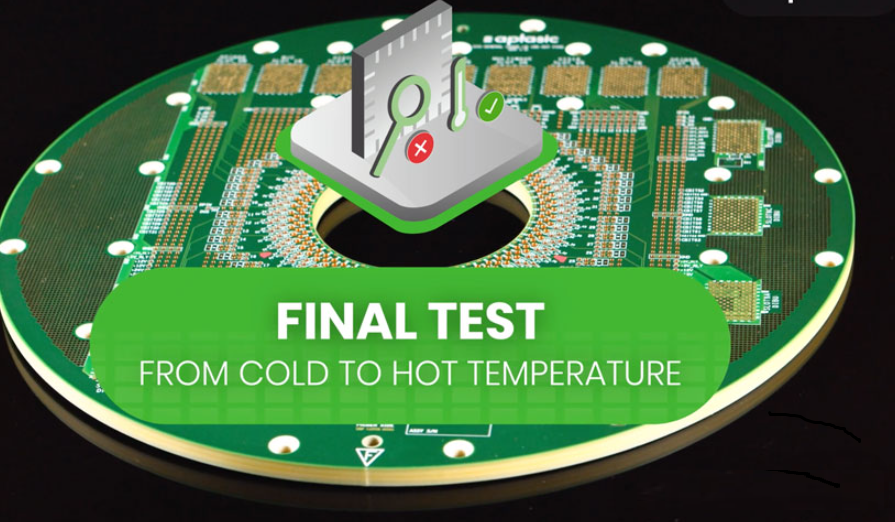

FT(การทดสอบครั้งสุดท้าย): เป็นการสกัดกั้นครั้งสุดท้ายก่อนที่ชิปจะออกจากโรงงาน วัตถุทดสอบมีไว้สำหรับชิปที่ห่อหุ้ม ซึ่งจะถูกห่อหุ้มหลังการทดสอบ CP และทดสอบ FT หลังจากการห่อหุ้ม สามารถใช้ทดสอบระดับเทคนิคของโรงงานบรรจุภัณฑ์ได้

CP สำหรับเวเฟอร์ ถ้า Die ไม่ดีไม่จำเป็นต้องทำบรรจุภัณฑ์ ช่วยประหยัดต้นทุนบรรจุภัณฑ์และต้นทุนพื้นผิว

หลังจากการทดสอบ CP เสร็จสิ้น ความล้มเหลวของชิปจะเกิดขึ้นในกระบวนการบรรจุภัณฑ์ ดังนั้น FT จึงจำเป็นต้องถอดชิปที่ล้มเหลวออกด้วย

อัตราผลตอบแทน: อัตราผลตอบแทนของชิปเกี่ยวข้องกับกระบวนการ ชิปมีความน่าจะเป็นที่จะล้มเหลว และยิ่งชิปมีขนาดใหญ่เท่าใด ความน่าจะเป็นที่จะล้มเหลวก็จะยิ่งมากขึ้นเท่านั้น

IP (ทรัพย์สินทางปัญญา):ในการออกแบบวงจรรวม หมายถึงโมดูลการทำงานที่สมบูรณ์ของวงจรรวมที่ได้รับการพิสูจน์แล้วและนำกลับมาใช้ใหม่ได้พร้อมฟังก์ชันเฉพาะ

การแบ่งประเภท IP สามารถแบ่งออกเป็นใบอนุญาต ความภักดีต่อลักษณะการเก็บค่าผ่านทาง

ใบอนุญาต การอนุญาตใบอนุญาต: การอนุญาตให้ใช้ IP นี้ การอนุญาตของ IP

ค่าลิขสิทธิ์สำหรับสมาชิก: หลังจากที่ผู้ใช้ใช้ IP แล้ว พวกเขาจะถูกเรียกเก็บเงินต่อชิป

IP เป็นองค์ประกอบหลักของชิป เช่น USB, PCIE, CPU คือ IP, ชิปทั้งหมดเป็นแบบรวม IP, ชิปสามารถทำงานได้ซับซ้อนมากขึ้น, แกนหลักคือการนำ IP มาใช้ซ้ำ ตัวอย่างเช่น ผู้สร้างประตูหลายสิบล้านประตู หลายร้อยล้านประตู สามารถนำ IP มาใช้ซ้ำได้

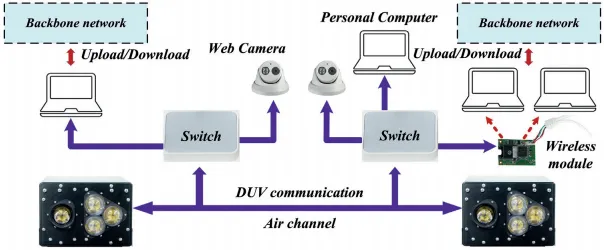

DUV (รังสีอัลตราไวโอเลตระดับลึก) EUV (รังสีอัลตราไวโอเลตรุนแรง)

บรรจุภัณฑ์

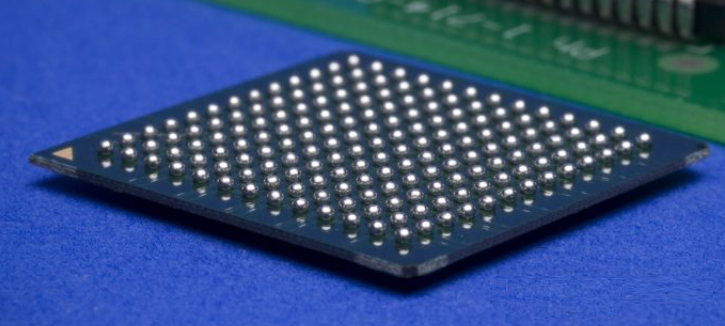

BGA (Ball Grid Array): ประเภทของแพ็คเกจที่ติดตั้งบนพื้นผิวซึ่งมีลูกบอลบัดกรีที่เชื่อมต่ออยู่จำนวนหนึ่งถูกจัดเรียงไว้บนพื้นผิวที่ติดตั้งชิป (อาร์เรย์กริดลูกบอล)

ASIC (วงจรรวมเฉพาะแอปพลิเคชัน): ASIC คือชิปพิเศษ ซึ่งเป็นคำทั่วไปสำหรับชิปที่ได้รับการปรับแต่งเป็นพิเศษสำหรับความต้องการเฉพาะ ตัวอย่างเช่น โปรเซสเซอร์เสียงและวิดีโอเฉพาะ และในปัจจุบัน อุตสาหกรรมชิป AI เฉพาะจำนวนมากถือได้ว่าเป็น ASIC ประเภทหนึ่ง

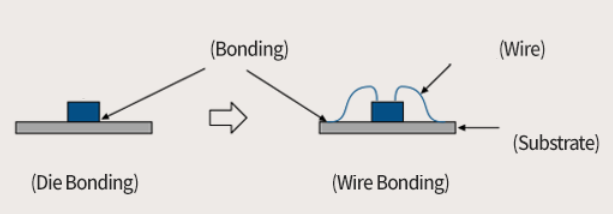

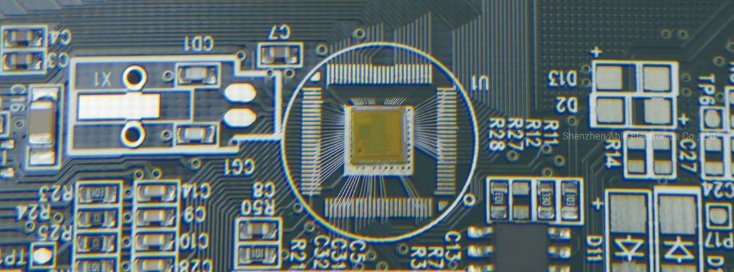

การเชื่อมแบบลวด: การเชื่อมด้วยลวด (การเชื่อมแบบกดหรือที่เรียกว่าการเชื่อมแบบเชื่อม การเชื่อมแบบลวด) หมายถึงการใช้ลวดโลหะ (ลวดทอง ลวดอลูมิเนียม... ฯลฯ) การใช้การกดร้อนหรือพลังงานอัลตราโซนิคเพื่อทำให้การเชื่อมต่อเสร็จสมบูรณ์ ของการเดินสายภายในของวงจรโซลิดสเตต กล่าวคือ การเชื่อมต่อระหว่างชิปกับวงจรหรือลีดเฟรม

ผูกพันตาย:

Flipchip: ลูกบอลตะกั่วดีบุกจะเกาะอยู่บน I/Opad จากนั้นชิปจะถูกพลิกกลับและให้ความร้อนโดยใช้ลูกบอลตะกั่วดีบุกหลอมรวมกับซับสเตรตเซรามิก

COB (ชิปบนบอร์ด):บรรจุภัณฑ์ชิปออนบอร์ดคือการติดชิปเปลือยเข้ากับ PCB ด้วยกาวที่เป็นสื่อกระแสไฟฟ้าหรือไม่นำไฟฟ้า จากนั้นจึงทำการติดตะกั่วเพื่อให้เกิดการเชื่อมต่อทางไฟฟ้า และห่อชิปและตะกั่วด้วยพันธะ กาว

SOC (ระบบบนชิป): คือการนำ CPU, บัส, อุปกรณ์ต่อพ่วง... ฯลฯ ไปใช้ภายในชิป ตัวอย่างเช่น โปรเซสเซอร์โทรศัพท์มือถือเป็นชิป SOC ที่ซับซ้อน

SIP (ระบบในแพ็คเกจ): แพ็คเกจ SiP คือชิปดิบที่มีฟังก์ชั่นที่แตกต่างกัน รวมถึง CPU, GPU, หน่วยความจำ... ฯลฯ รวมอยู่ในตัวแพ็คเกจเพื่อให้ได้ระบบชิปทั้งหมด

SOP (แพ็คเกจโครงร่างเล็ก):แพ็คเกจภายนอกขนาดเล็กของแพ็คเกจ IC ซึ่งสายสัญญาณจะถูกดึงทั้งสองทิศทาง

DAF (Die Attach Film): เทคโนโลยีการติดฟิล์มพันธะเวเฟอร์

CMOS (สารกึ่งตัวนำโลหะออกไซด์เสริม): สารกึ่งตัวนำโลหะออกไซด์เสริม หมายถึงเทคโนโลยีที่ใช้สร้างชิปวงจรรวมขนาดใหญ่หรือชิปที่ผลิตโดยใช้เทคโนโลยีนี้ซึ่งเป็นชิ้นส่วนของชิป RAM ที่สามารถอ่านและเขียนบนเมนบอร์ดของคอมพิวเตอร์ได้ เนื่องจากคุณลักษณะการอ่าน-เขียน จึงใช้เพื่อบันทึกข้อมูล BIOS หลังจากตั้งค่าพารามิเตอร์ฮาร์ดแวร์คอมพิวเตอร์บนเมนบอร์ดคอมพิวเตอร์แล้ว และชิปนี้ใช้สำหรับจัดเก็บข้อมูลเท่านั้น

JEDEC (มาตรฐานสภาวิศวกรรมอุปกรณ์อิเล็กตรอนร่วม): ข้อกำหนดมาตรฐานของสหรัฐอเมริกาสำหรับขนาดบรรจุภัณฑ์

Fountyl Technologies PTE Ltd มุ่งเน้นไปที่อุตสาหกรรมการผลิตเซมิคอนดักเตอร์ ผลิตภัณฑ์หลัก ได้แก่: Pin chuck, หัวจับเซรามิกที่มีรูพรุน, เอฟเฟกต์ปลายเซรามิก, คานสี่เหลี่ยมเซรามิก, แกนหมุนเซรามิก ยินดีต้อนรับสู่การติดต่อและการเจรจา!