วิธีแก้ปัญหาการกระจายความร้อนของแพ็คเกจชิป

ชิปบรรจุภัณฑ์ขั้นสูงไม่เพียงแต่สามารถตอบสนองความต้องการของคอมพิวเตอร์ประสิทธิภาพสูง ปัญญาประดิษฐ์ การเติบโตของความหนาแน่นของพลังงาน ฯลฯ เท่านั้น แต่ยังรวมถึงปัญหาการกระจายความร้อนของบรรจุภัณฑ์ขั้นสูงที่มีความซับซ้อนอีกด้วย เนื่องจากฮอตสปอตบนชิปตัวเดียวส่งผลต่อการกระจายความร้อนของชิปข้างเคียง การเชื่อมต่อระหว่างชิปยังช้ากว่าในโมดูลมากกว่าใน SoC

John Parry หัวหน้าฝ่ายอุตสาหกรรมอิเล็กทรอนิกส์และเซมิคอนดักเตอร์ของ Siemens Digital Industry Software กล่าวว่า "ก่อนที่โลกจะย้ายเข้าสู่พื้นที่เช่นมัลติคอร์ คุณกำลังเผชิญกับชิปที่มีกำลังสูงสุดประมาณ 150 วัตต์ต่อตารางเซนติเมตร ซึ่ง แหล่งความร้อนจุดเดียว คุณสามารถกระจายความร้อนได้ทั้งสามทิศทาง ดังนั้น คุณจึงสามารถได้รับพลังงานที่มีความหนาแน่นค่อนข้างสูง แต่เมื่อคุณมีชิป ให้วางชิปอีกอันไว้ข้างๆ แล้ววางชิปอีกอันไว้ข้างๆ มันจะร้อนขึ้น นั่นหมายความว่าคุณไม่สามารถทนต่อชิปแต่ละตัวที่มีระดับพลังงานเท่ากันได้ ซึ่งทำให้ความท้าทายด้านความร้อนยากขึ้นมาก"

นี่เป็นหนึ่งในสาเหตุหลักที่ทำให้ 3D-IC Stacking มีความคืบหน้าช้าในตลาด แม้ว่าแนวคิดนี้จะดูสมเหตุสมผลจากประสิทธิภาพการใช้พลังงานและจุดยืนในการบูรณาการ และทำงานได้ดีใน 3D NAND และ HBM แต่เมื่อรวมตรรกะเข้าไปด้วย จะเป็นอีกเรื่องหนึ่ง ชิปลอจิกจะสร้างความร้อน และยิ่งตรรกะมีความหนาแน่นมากขึ้น การใช้องค์ประกอบการประมวลผลก็จะยิ่งสูง ความร้อนก็จะยิ่งมากขึ้นตามไปด้วย สิ่งนี้ทำให้การซ้อนแบบลอจิคัลเกิดขึ้นได้ยาก

เลือกแพ็คเกจที่เหมาะสม

สำหรับนักออกแบบชิป มีหลายวิธีในการบรรจุหีบห่อ แต่ประสิทธิภาพของการรวมชิปเป็นสิ่งสำคัญ ส่วนประกอบต่างๆ เช่น คอลัมน์ซิลิคอน TSV และทองแดงล้วนมีค่าสัมประสิทธิ์การขยายตัวเนื่องจากความร้อน (TCE) ที่แตกต่างกัน ซึ่งส่งผลต่อผลผลิตในการประกอบและความน่าเชื่อถือในระยะยาว

แพ็คเกจ Flip BGA ยอดนิยมในปัจจุบันที่มี CPU และ HBM มีพื้นที่ประมาณ 2,500 ตารางมิลลิเมตร Mike McIntyre หัวหน้าฝ่ายการจัดการผลิตภัณฑ์ซอฟต์แวร์ของ Onto Innovation กล่าวว่า "เราเห็นชิปขนาดใหญ่ที่อาจกลายเป็นชิปขนาดเล็กสี่หรือห้าชิป ดังนั้นคุณต้องมี I/O มากขึ้นเพื่อให้ชิปเหล่านี้สื่อสารกันได้ ดังนั้นคุณจึงสามารถกระจายความร้อนได้ ท้ายที่สุดแล้ว การกระจายความร้อนเป็นปัญหาที่สามารถแก้ไขได้ในระดับระบบเท่านั้น และมาพร้อมกับข้อด้อยต่างๆ มากมาย

ในความเป็นจริง อุปกรณ์บางอย่างมีความซับซ้อนมากจนเป็นการยากที่จะเปลี่ยนส่วนประกอบได้อย่างง่ายดายเพื่อปรับแต่งอุปกรณ์เหล่านี้สำหรับแอปพลิเคชันในสาขาเฉพาะ นี่คือเหตุผลว่าทำไมผลิตภัณฑ์บรรจุภัณฑ์ขั้นสูงจำนวนมากจึงมีไว้สำหรับส่วนประกอบที่มีปริมาณมากหรือมีความยืดหยุ่นด้านราคา เช่น ชิปเซิร์ฟเวอร์

ความคืบหน้าในการจำลองและการทดสอบโมดูลชิป

อย่างไรก็ตาม วิศวกรกำลังมองหาวิธีใหม่ๆ ในการทำการวิเคราะห์เชิงความร้อนของความน่าเชื่อถือของบรรจุภัณฑ์ก่อนที่จะผลิตโมดูลที่บรรจุหีบห่อ ตัวอย่างเช่น Siemens ได้จัดเตรียมตัวอย่างของโมดูลที่ใช้ ASIC แบบคู่ ซึ่งติดตั้ง Fan-out Redistribution Layer (RDL) บนพื้นผิวอินทรีย์หลายชั้นในแพ็คเกจ BGA ใช้สองรุ่น รุ่นหนึ่งสำหรับ WLP ที่ใช้ RDL และอีกรุ่นสำหรับ BGA สารตั้งต้นอินทรีย์หลายชั้น โมเดลบรรจุภัณฑ์เหล่านี้ได้รับการกำหนดพารามิเตอร์ รวมถึงการซ้อนซับสเตรตและ BGA ก่อนที่จะแนะนำข้อมูล EDA และช่วยให้สามารถประเมินวัสดุและการเลือกตำแหน่งชิปได้ตั้งแต่เนิ่นๆ ถัดไป ข้อมูล EDA จะถูกนำเข้า และสำหรับแต่ละรุ่น ผังวัสดุสามารถให้คำอธิบายเชิงความร้อนโดยละเอียดของการกระจายตัวของทองแดงในทุกชั้น

Eric Ouyang ผู้อำนวยการฝ่ายการตลาดทางเทคนิคของ JCET ร่วมกับวิศวกรจาก JCET และ Meta เปรียบเทียบประสิทธิภาพการระบายความร้อนของโมดูลชิปเดี่ยว, หลายชิป, ปลั๊กบอร์ด 2.5D และชิปสแต็ก 3D กับ ASIC หนึ่งตัวและ Sram สองอัน [1] การเปรียบเทียบระหว่าง Apple กับ Apple ทำให้สภาพแวดล้อมของเซิร์ฟเวอร์ หม้อน้ำพร้อมช่องสุญญากาศ และ TIM ไม่เปลี่ยนแปลง ในแง่ของความร้อน 2.5D และ MCM ทำงานได้ดีกว่าชิป 3D หรือชิปตัวเดียว

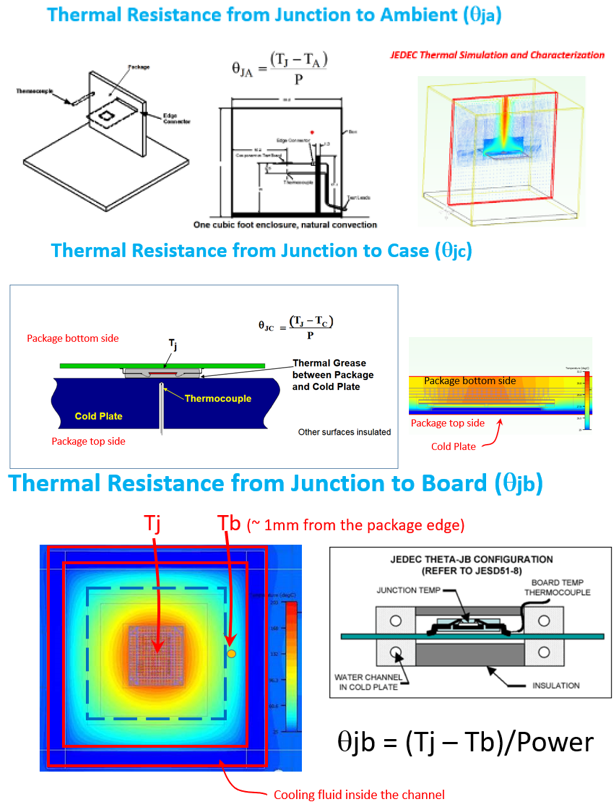

ความต้านทานความร้อนเชิงปริมาณ

เราสามารถเข้าใจวิธีการนำความร้อนผ่านชิปซิลิคอน แผงวงจร กาว TIM หรือฝาบรรจุภัณฑ์ ขณะเดียวกันก็ใช้วิธีการมาตรฐานสำหรับความแตกต่างของอุณหภูมิและฟังก์ชันพลังงานเพื่อติดตามค่าอุณหภูมิและความต้านทาน

"เส้นทางความร้อนจะถูกวัดปริมาณด้วยค่าหลักสามค่า ได้แก่ ความต้านทานความร้อนจากโหนดอุปกรณ์ไปยังสภาพแวดล้อม ความต้านทานความร้อนจากโหนดไปยังตัวเครื่อง [ที่ด้านบนของบรรจุภัณฑ์] และความต้านทานความร้อนจากโหนดไปยังบอร์ด ” Ouyang จาก JCET กล่าว อย่างน้อยที่สุด เขาชี้ให้เห็นว่า ลูกค้าของ JCET ต้องการ ɵja, ɵjc และ ɵjb ซึ่งพวกเขาจะใช้ในการออกแบบระบบ พวกเขาอาจต้องการให้ความต้านทานความร้อนที่กำหนดไม่เกินค่าเฉพาะและการออกแบบบรรจุภัณฑ์ให้ประสิทธิภาพนั้น

การจำลองความร้อนเป็นวิธีที่ประหยัดที่สุดในการสำรวจการเลือกและการจัดเรียงวัสดุ จากการจำลองชิปในสถานะการทำงาน เรามักจะพบจุดร้อนอย่างน้อยหนึ่งจุด ดังนั้นเราจึงสามารถเพิ่มทองแดงลงในสารตั้งต้นด้านล่างจุดร้อนเพื่ออำนวยความสะดวกในการกระจายความร้อน หรือเปลี่ยนวัสดุบรรจุภัณฑ์เพิ่มหม้อน้ำ ผู้ประกอบระบบอาจระบุว่าความต้านทานความร้อน ɵja, ɵjc และ ɵjb ต้องไม่เกินค่าที่กำหนด ภายใต้สถานการณ์ปกติ ควรรักษาอุณหภูมิจุดเชื่อมต่อซิลิคอนให้ต่ำกว่า 125 ° C หลังจากการจำลองเสร็จสิ้น โรงงานบรรจุภัณฑ์จะดำเนินการออกแบบการทดลอง (DOE) เพื่อให้ได้แผนบรรจุภัณฑ์ขั้นสุดท้าย

เลือก ทิม

ในบรรจุภัณฑ์ ความร้อนมากกว่า 90% จะถูกกระจายผ่านบรรจุภัณฑ์จากด้านบนของชิปไปยังหม้อน้ำ ซึ่งโดยปกติจะเป็นครีบแนวตั้งที่ทำจากอลูมิเนียมอโนไดซ์ วัสดุเชื่อมต่อในการระบายความร้อน (TIM) ที่มีค่าการนำความร้อนสูงจะถูกวางไว้ระหว่างชิปและบรรจุภัณฑ์เพื่อช่วยถ่ายเทความร้อน TIM ยุคใหม่สำหรับซีพียูประกอบด้วยโลหะผสมแผ่น เช่น อินเดียมและดีบุก รวมถึงดีบุกเผาผนึกเงินที่มีค่าการนำไฟฟ้า 60W/mK และ 50W/mK ตามลำดับ ในขณะที่ผู้จำหน่ายเปลี่ยน SoC ไปใช้กระบวนการชิปเล็ต จำเป็นต้องมี TIM ที่มีคุณสมบัติและความหนาต่างกันมากขึ้น

YoungDo Kweon ผู้อำนวยการอาวุโสฝ่ายวิจัยและพัฒนาที่ Amkor กล่าวว่าสำหรับระบบที่มีความหนาแน่นสูง ความต้านทานความร้อนของ TIM ระหว่างชิปและบรรจุภัณฑ์มีผลกระทบมากขึ้นต่อความต้านทานความร้อนโดยรวมของโมดูลที่บรรจุ แนวโน้มพลังงานกำลังเพิ่มขึ้นอย่างมาก โดยเฉพาะในด้านลอจิก ดังนั้นเราจึงมุ่งเน้นไปที่การรักษาอุณหภูมิจุดเชื่อมต่อให้ต่ำเพื่อให้แน่ใจว่าการทำงานของเซมิคอนดักเตอร์เชื่อถือได้ แม้ว่าซัพพลายเออร์ของ TIM จะให้ค่าความต้านทานความร้อนสำหรับวัสดุของตน แต่ในความเป็นจริงแล้ว ความต้านทานความร้อนจากชิปถึงบรรจุภัณฑ์ (ɵjc) จะได้รับผลกระทบจากกระบวนการประกอบเอง รวมถึงคุณภาพการยึดเกาะและพื้นที่สัมผัสระหว่างชิปและ TIM เขาตั้งข้อสังเกตว่าการทดสอบด้วยเครื่องมือประกอบจริงและวัสดุประสานในสภาพแวดล้อมที่มีการควบคุมมีความสำคัญอย่างยิ่งในการทำความเข้าใจคุณสมบัติทางความร้อนที่แท้จริงและการเลือก TIM ที่ดีที่สุดสำหรับการตรวจสอบลูกค้า

เพื่อจัดการกับความร้อนในรูปแบบต่างๆ

ผู้ผลิตชิปกำลังมองหาวิธีแก้ปัญหาการกระจายความร้อน Randy White ผู้จัดการโปรแกรมสำหรับโซลูชันหน่วยความจำของ Keysight Technologies กล่าวว่า "แพ็คเกจจะเหมือนเดิม หากคุณลดพื้นที่ขนาดชิปลงหนึ่งในสี่ก็จะเร็วขึ้น ซึ่งอาจส่งผลให้ความสมบูรณ์ของสัญญาณมีความแตกต่างกัน เนื่องจากเส้นพันธะ ของแพ็คเกจภายนอกจะเข้าสู่ชิป ยิ่งเส้นยาว ยิ่งมีความเหนี่ยวนำมากขึ้น จึงมีชิ้นส่วนประสิทธิภาพทางไฟฟ้า แล้วคุณจะใช้พลังงานขนาดนั้นในพื้นที่เล็ก ๆ เพียงพอได้อย่างไร นี่คืออีกหนึ่งพารามิเตอร์สำคัญที่ต้องเป็น ศึกษาแล้ว” สิ่งนี้นำไปสู่การลงทุนที่สำคัญในการวิจัยพันธะที่ล้ำสมัยซึ่งดูเหมือนจะมุ่งเน้นไปที่พันธะลูกผสม แต่ต้นทุนของการเชื่อมแบบไฮบริดนั้นสูง และยังคงจำกัดอยู่เพียงแอปพลิเคชันประเภทตัวประมวลผลประสิทธิภาพสูง โดย TSMC เป็นหนึ่งในบริษัทเดียวที่นำเสนอเทคโนโลยีนี้ในปัจจุบัน อย่างไรก็ตาม โอกาสในการรวมโฟตอนบนชิป CMOS หรือแกลเลียมไนไตรด์ที่ใช้ซิลิคอนมีแนวโน้มที่ดีมาก

Fountyl Technologies PTE Ltd มุ่งเน้นไปที่อุตสาหกรรมการผลิตเซมิคอนดักเตอร์ ผลิตภัณฑ์หลัก ได้แก่: Pin chuck, หัวจับเซรามิกที่มีรูพรุน, เอฟเฟกต์ปลายเซรามิก, คานสี่เหลี่ยมเซรามิก, แกนหมุนเซรามิก ยินดีต้อนรับสู่การติดต่อและการเจรจา!