Làm thế nào để giải quyết vấn đề tản nhiệt gói chip

Chip đóng gói tiên tiến không chỉ có thể đáp ứng nhu cầu tính toán hiệu năng cao, trí tuệ nhân tạo, tăng trưởng mật độ năng lượng, v.v. mà vấn đề tản nhiệt của bao bì tiên tiến cũng trở nên phức tạp. Bởi vì các điểm nóng trên một chip ảnh hưởng đến sự phân bổ nhiệt của các chip lân cận. Sự kết nối giữa các chip trong mô-đun cũng chậm hơn so với SoC.

John Parry, người đứng đầu ngành điện tử và bán dẫn tại Phần mềm Công nghiệp Kỹ thuật số Siemens, cho biết: "Trước khi thế giới chuyển sang các lĩnh vực như đa lõi, bạn đang xử lý một con chip có công suất tối đa khoảng 150 watt trên mỗi cm vuông, tức là một nguồn nhiệt điểm duy nhất Bạn có thể tản nhiệt theo cả ba hướng, do đó bạn có thể đạt được mật độ năng lượng khá cao. Nhưng khi bạn có một con chip, hãy đặt một con chip khác bên cạnh nó, rồi đặt một con chip khác bên cạnh nó, chúng sẽ nóng lên. nhau, điều đó có nghĩa là bạn không thể chịu đựng được mỗi con chip có cùng mức năng lượng, điều này khiến thách thức về nhiệt trở nên khó khăn hơn nhiều.”

Đây là một trong những lý do chính khiến việc xếp chồng 3D-IC đang tiến triển chậm trên thị trường. Mặc dù khái niệm này có ý nghĩa từ quan điểm tích hợp và hiệu quả năng lượng - và hoạt động tốt trong 3D NAND và HBM - nhưng khi đưa logic vào thì lại là một câu chuyện khác. Chip logic tạo ra nhiệt và logic càng dày đặc thì việc sử dụng các phần tử xử lý càng cao thì nhiệt càng lớn. Điều này làm cho việc xếp chồng logic trở nên hiếm gặp.

Chọn gói phù hợp

Đối với các nhà thiết kế chip, có rất nhiều cách để đóng gói. Nhưng hiệu suất tích hợp chip là rất quan trọng. Các thành phần như cột silicon, TSV và đồng đều có hệ số giãn nở nhiệt (TCE) khác nhau, ảnh hưởng đến năng suất lắp ráp và độ tin cậy lâu dài.

Gói BGA lật phổ biến hiện nay với cpu và HBM có diện tích khoảng 2500 mm vuông. Mike McIntyre, người đứng đầu bộ phận quản lý sản phẩm phần mềm tại Onto Innovation, cho biết: “Chúng tôi đang thấy một con chip lớn có khả năng trở thành bốn hoặc năm con chip nhỏ. Vì vậy, bạn phải có nhiều I/O hơn để những con chip này giao tiếp với nhau. Vì vậy, bạn có thể phân phối nhiệt. Cuối cùng, tản nhiệt là một vấn đề chỉ có thể được giải quyết ở cấp độ hệ thống và nó đi kèm với một loạt sự đánh đổi.

Trên thực tế, một số thiết bị phức tạp đến mức khó có thể dễ dàng thay thế các thành phần để tùy chỉnh các thiết bị này cho các ứng dụng trong các lĩnh vực cụ thể. Đây là lý do tại sao nhiều sản phẩm đóng gói tiên tiến dành cho các thành phần có khối lượng rất lớn hoặc co giãn về giá, chẳng hạn như chip máy chủ.

Tiến bộ trong mô phỏng và thử nghiệm mô-đun chip

Tuy nhiên, các kỹ sư đang tìm kiếm những cách mới để thực hiện phân tích nhiệt về độ tin cậy của gói trước khi sản xuất các mô-đun đóng gói. Ví dụ: Siemens cung cấp một ví dụ về mô-đun dựa trên ASIC kép cài đặt lớp phân phối lại quạt ra (RDL) trên chất nền hữu cơ nhiều lớp trong gói BGA. Nó sử dụng hai mô hình, một cho WLP dựa trên RDL và một cho BGA chất nền hữu cơ nhiều lớp. Các mô hình đóng gói này được tham số hóa, bao gồm xếp chồng chất nền và BGA trước khi thông tin EDA được đưa ra, đồng thời cho phép đánh giá vật liệu sớm và lựa chọn vị trí chip. Tiếp theo, dữ liệu EDA được nhập và đối với mỗi mô hình, bản đồ vật liệu có thể cung cấp mô tả nhiệt chi tiết về sự phân bổ đồng trong tất cả các lớp.

Eric Ouyang, Giám đốc Tiếp thị Kỹ thuật tại JCET, cùng với các kỹ sư từ JCET và Meta, đã so sánh hiệu suất nhiệt của các mô-đun đơn chip, đa chip, bảng mạch 2,5D và chip xếp chồng 3D với một ASIC và hai Sram. [1] So sánh giữa Apple và Apple khiến môi trường máy chủ, bộ tản nhiệt có buồng chân không và TIM không thay đổi. Về mặt nhiệt, 2.5D và MCM hoạt động tốt hơn so với chip 3D hoặc chip đơn.

Điện trở nhiệt lượng tử hóa

Chúng ta có thể hiểu cách truyền nhiệt thông qua chip silicon, bảng mạch, keo dán, TIM hoặc nắp đóng gói, đồng thời sử dụng phương pháp tiêu chuẩn về chênh lệch nhiệt độ và hàm công suất để theo dõi các giá trị nhiệt độ và điện trở.

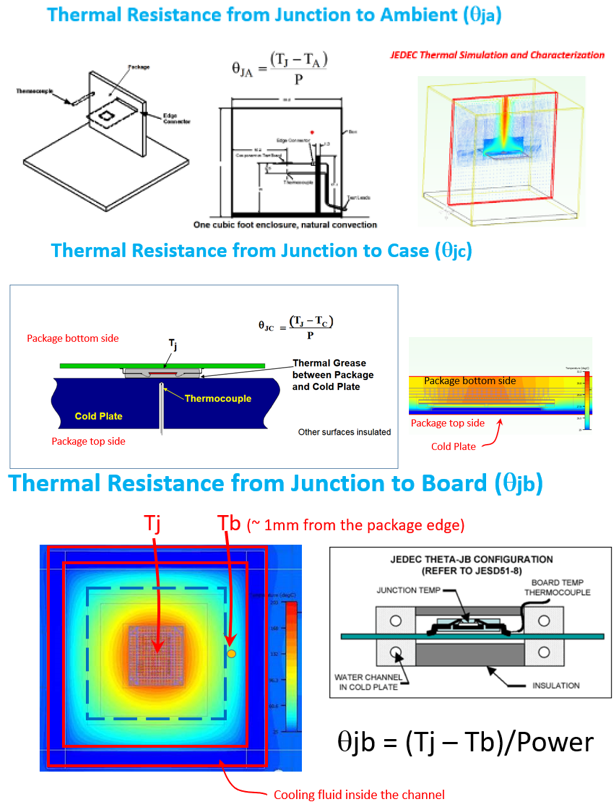

"Đường dẫn nhiệt được định lượng bằng ba giá trị chính - điện trở nhiệt từ nút thiết bị đến môi trường, điện trở nhiệt từ nút đến vỏ [ở đầu gói] và điện trở nhiệt từ nút đến bảng ", Ouyang của JCET nói. Ông chỉ ra rằng ít nhất, khách hàng của JCET cần ɵja, ɵjc và ɵjb, sau đó họ sử dụng những từ này trong thiết kế hệ thống. Họ có thể yêu cầu điện trở nhiệt nhất định không vượt quá một giá trị cụ thể và thiết kế bao bì phải đảm bảo hiệu suất đó.

Mô phỏng nhiệt là cách tiết kiệm nhất để khám phá việc lựa chọn và sắp xếp vật liệu. Thông qua việc mô phỏng chip ở trạng thái hoạt động, chúng ta thường tìm thấy một hoặc nhiều điểm nóng, vì vậy chúng ta có thể thêm đồng vào đế bên dưới điểm nóng để tạo điều kiện tản nhiệt; Hoặc thay đổi chất liệu bao bì, tăng bộ tản nhiệt. Nhà tích hợp hệ thống có thể chỉ định rằng điện trở nhiệt ɵja, ɵjc và ɵjb không được vượt quá các giá trị nhất định. Trong trường hợp bình thường, nhiệt độ điểm nối silicon phải được giữ dưới 125 ° C. Sau khi mô phỏng hoàn tất, nhà máy đóng gói tiến hành thiết kế thí nghiệm (DOE) để đi đến kế hoạch đóng gói cuối cùng.

Chọn THỜI GIAN

Trong gói, hơn 90% nhiệt lượng được tiêu tán qua gói từ đỉnh chip đến bộ tản nhiệt, thường là một cánh tản nhiệt thẳng đứng làm bằng nhôm anodized. Vật liệu giao diện nhiệt (TIM) có tính dẫn nhiệt cao được đặt giữa chip và gói để giúp truyền nhiệt. TIM thế hệ tiếp theo dành cho CPU bao gồm các hợp kim kim loại tấm như indium và thiếc, cũng như thiếc thiêu kết bạc có độ dẫn điện lần lượt là 60W/mK và 50W/mK. Khi các nhà cung cấp chuyển đổi SoC sang quy trình chiplet, cần có nhiều TIM hơn với các đặc tính và độ dày khác nhau.

YoungDo Kweon, giám đốc nghiên cứu và phát triển cấp cao tại Amkor, cho biết đối với các hệ thống mật độ cao, khả năng chịu nhiệt của TIM giữa chip và gói có tác động lớn hơn đến khả năng chịu nhiệt tổng thể của mô-đun đóng gói. Xu hướng nguồn điện đang tăng lên đáng kể, đặc biệt là đối với logic, vì vậy chúng tôi tập trung vào việc giữ nhiệt độ tiếp giáp ở mức thấp để đảm bảo chất bán dẫn hoạt động đáng tin cậy. Mặc dù các nhà cung cấp TIM cung cấp các giá trị điện trở nhiệt cho vật liệu của họ nhưng trên thực tế, điện trở nhiệt từ chip đến gói (ɵjc) bị ảnh hưởng bởi chính quá trình lắp ráp, bao gồm chất lượng liên kết và diện tích tiếp xúc giữa chip và TIM. Ông lưu ý rằng việc thử nghiệm bằng các công cụ lắp ráp thực tế và vật liệu liên kết trong môi trường được kiểm soát là rất quan trọng để hiểu được các đặc tính nhiệt thực tế và chọn TIM tốt nhất để xác minh của khách hàng.

Để đối phó với nhiệt theo những cách khác nhau

Các nhà sản xuất chip đang tìm cách giải quyết vấn đề tản nhiệt. Randy White, giám đốc chương trình giải pháp bộ nhớ tại Keysight Technologies, cho biết: “Gói này giống nhau, nếu bạn giảm diện tích kích thước chip xuống một phần tư thì tốc độ sẽ tăng lên. Điều này có thể dẫn đến một số khác biệt về tính toàn vẹn tín hiệu. Bởi vì đường liên kết của gói bên ngoài sẽ đi vào chip, đường dây càng dài thì độ tự cảm càng lớn, do đó có một phần hiệu suất điện vậy làm thế nào để bạn tiêu thụ được nhiều năng lượng như vậy trong một không gian đủ nhỏ. Đây là một thông số quan trọng khác cần phải có. đã học." Điều này đã dẫn đến sự đầu tư đáng kể vào nghiên cứu liên kết tiên tiến dường như tập trung vào liên kết lai. Tuy nhiên, chi phí của liên kết lai cao và nó vẫn bị giới hạn ở các ứng dụng loại bộ xử lý hiệu suất cao, trong đó TSMC là một trong những công ty duy nhất hiện đang cung cấp công nghệ này. Tuy nhiên, triển vọng kết hợp các photon trên chip CMOS hoặc gallium nitride dựa trên silicon là rất hứa hẹn.

Fountyl Technologies PTE Ltd, đang tập trung vào ngành sản xuất chất bán dẫn, các sản phẩm chính bao gồm: Mâm cặp chốt, mâm cặp gốm xốp, bộ tác động cuối bằng gốm, dầm vuông gốm, trục chính bằng gốm, vui lòng liên hệ và đàm phán!